## EAST WEST UNIVERSITY

## "Effect of Quantum Mechanical Correction on Drain Current of Ultra Thin Body SOI MOSFET."

By

### Mustafa

Said Imam

In partial fulfillment of the requirements for the degree of Bachelor of Science in Electrical & Electronic Engineering

**Summer, 2012**

Department of Electrical & Electronic Engineering Faculty of science and engineering East West University

# Effect of Quantum Mechanical Correction on Drain Current of Ultra Thin Body SOI MOSFET.

By

Mustafa

Said Imam

Submitted to the Department of Electrical & Electronic Engineering Faculty of science and engineering East West University

In partial fulfillment of the requirements for the degree of

Bachelor of Science in Electrical & Electronic Engineering

(B.Sc. in EEE)

Summer, 2012

Thesis Advisor Dr. Anisul Haque Chairperson Dr. Mohammad Mojammel Al Hakim

#### Abstract

Impact of Ouantum Mechanical correction in surface potential based compact model on the drain current of UTB SOI MOSFET is studied here. Drain current of FD SOI MOSFET is also observed here. As surface potential based compact model we have selected such a model which incorporate the effect of substrate charge explicitly and it also assumed that the silicon film is always fully depleted and the back silicon film surface is never inverted. We have considered a QM correction model (which is basically used in nanoscale MOSFETs) to the surface potential based compact model of Karim and Haque where the effect of wave function penetration into the gate dielectric is taken into account. In our work we have incorporated the effect of this correction on the drain current characteristics of UTB SOI MOSFET. After the inclusion of QM correction in to the front surface potential ( $\phi_{sf}$ ) of UTB SOI MOSFET increase of  $\phi_{sf}$  is observed. Furthermore, QM correction of  $\phi_{sf}$  shows the decrease of drain current of the UTB SOI MOSFET in comparison with the drain current obtain from the semi-classical compact model. For UTB SOI MOSFET, before including QM correction to  $\phi_{sf}$ , a maximum relative error of about 0.6% is obtained between the analytical solution of three surface potentials and iterative solution of exact Poisson equations. In strong inversion, the percentage deviation between saturated drain current of the semiclassical model and quantum corrected model is around 12 - 16%.

First of all, we are grateful to the Almighty Allah for giving us this opportunity to complete the research. Then we are grateful to our parents for their incomparable support.

We would like to thank Dr. Anisul Haque, professor, Department of Electrical and Electronic Engineering (EEE), East West University (EWU), Dhaka, our supervisor, for his regular guidance, supervision, constructive suggestions and constant support during this research.

We would also like to thank our former chairperson Dr. Khairul Alam and present chairperson Dr. Mohammad Mojammel Al Hakim, associate professor Department of EEE, EWU, Dhaka.

We also thank to all of our friends and well wishers for their moral support and helpful discussion during this thesis.

#### Approval

The thesis titled "Effect of Quantum Mechanical Correction on Drain Current of Ultra Thin Body SOI MOSFET" submitted by Mustafa (2008-3-80-011), Said Imam (2009-1-80-048), session summer, 2012, has been accepted satisfactory in partial fulfillment of requirement of the degree of Bachelor of Science in Electrical and Electronic Engineering on August, 2012.

Supervisor

Dr. Anisul Haque

Professor

Department of Electrical and Electronic Engineering,

East West University (EWU),

Dhaka-1212, Bangladesh

We hereby declare that we are the solo author of this thesis. We authorize East West University to lend this thesis to other institution or individuals for the purpose of scholarly research.

Mustafa (SID: 2008-3-80-011) Said Imam (SID: 2009-1-80-048)

We further authorize East West University to reproduce this thesis by photocopy or other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Mustafa (SID: 2008-3-80-011) Said Imam (SID: 2009-1-80-048)

| Abstract                                                                       | .ii |

|--------------------------------------------------------------------------------|-----|

| Acknowledgement                                                                | iii |

| Approval                                                                       |     |

| Authorization page                                                             |     |

| Chapter 1                                                                      |     |

| Introduction 1.1 Background                                                    |     |

|                                                                                |     |

| 1.2   Literature Review                                                        |     |

| 1.3 Objective                                                                  | .4  |

| 1.4 Organization of the thesis                                                 | .4  |

| Chapter 2                                                                      | .5  |

| Surface Potential Based Model for FD SOI MOSFET                                |     |

| 2.1 Appreciation of the Surface Potential Based Model                          | .5  |

| 2.2 Introduction to Fully Depleted SOI structure                               | .6  |

| 2.3 Effect of substrate charge on the Surface Potential                        | .6  |

| 2.4 Analytical Solution of Surface Potential                                   | .8  |

| 2.4.1 SURFACE POTENTIAL SOLUTION:                                              | 10  |

| 2.4.2 Weak inversion:                                                          | 10  |

| 2.4.3 Strong Inversion:                                                        | 12  |

| 2.4.4 Single piece model                                                       | 13  |

| 2.5 Surface Potential based drain current model                                | 13  |

| Chapter 3                                                                      | 15  |

| Quantum Mechanical Effect                                                      |     |

| 3.1 Energy quantization in the Silicon film due to quantum mechanical effects  | 15  |

| 3.1.1 Threshold Voltage shift                                                  | 16  |

| 3.1.2 Shift in surface potential                                               | 16  |

| 3.2 Quantum Mechanical Correction to the Surface Potential of Nanoscale FD SOI |     |

| MOSFETs                                                                        | 17  |

| 3.2.1 Basic approach of the Karim and Haque QM model                           | 17  |

| 3.2.2 Derivation of a mathematical expression of the proposed QM model         | 19  |

| Chapter 4                                                                      | 21  |

| Results and Discussion                                                         | 21  |

| 4.1 Surface Potential                                                          | 21  |

| 4.2 Drain Current                                                              | 25  |

| Chapter 5                                                                      | 28  |

| Summary                                                                        |     |

## **Table of Contents**

| 5.1     | Conclusion  | 28 |

|---------|-------------|----|

| 5.2     | Future Work | 28 |

| Append  | lix         | 30 |

| Referen | ces         | 37 |

## List of Figures

| Figure 2.1: Energy Band Diagram for Depletion mode5                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.2: Cross-sectional view of the FD SOI MOSFET7                                                                                 |

| Figure 2.3: Substrate surface potential $\phi_{sbulk}$ versus gate voltage for different substrate                                     |

| doping7                                                                                                                                |

| Figure 2.4: Electric field shape from the Si/SiO <sub>2</sub> interface of the front gate oxide toward the                             |

| substrate. The solid lines specify the electric field distribution for a given gate voltage. The                                       |

| dashed lines express the electric field when the silicon film is just depleted9                                                        |

| Figure 2.5: Surface potential vs Gate voltage                                                                                          |

| Figure 3.1: Discrete energy levels due to quantization (in the substrate)                                                              |

| Figure 3.2: Electron concentration distribution in the silicon substrate in classical and                                              |

| quantum mechanical cases                                                                                                               |

| Figure 4.1: For FD SOI, comparison of $\phi_{sf}$ obtained iteratively and analytically. Here,                                         |

| $t_{soi} = 25 \text{ nm}$ and $t_{box} = 50 \text{ nm}$                                                                                |

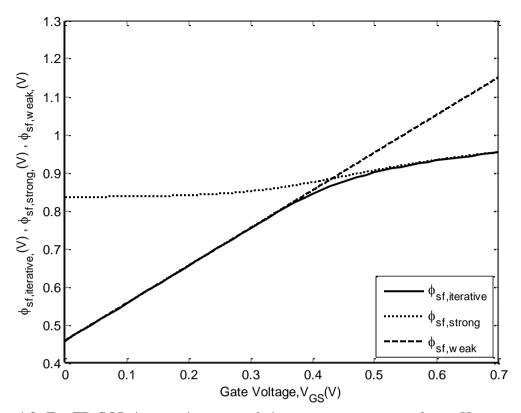

| Figure 4.2: For FD SOI, $\phi_{sf,weak}$ , $\phi_{sf,strong}$ , and $\phi_{sf,iterative}$ versus gate voltage. Here, $t_{soi} = 25$ nm |

| and $t_{box} = 50 \text{ nm}$                                                                                                          |

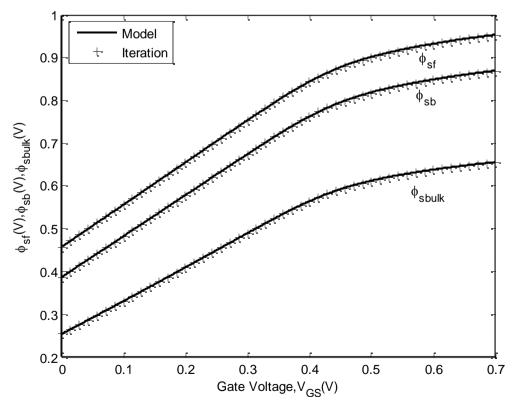

| Figure 4.3: For FD SOI, three surface potentials $\phi_{sf}$ , $\phi_{sb}$ , and $\phi_{sbulk}$ versus gate voltage. Here,             |

| $t_{soi} = 25 \text{ nm and } t_{box} = 50 \text{ nm}.$                                                                                |

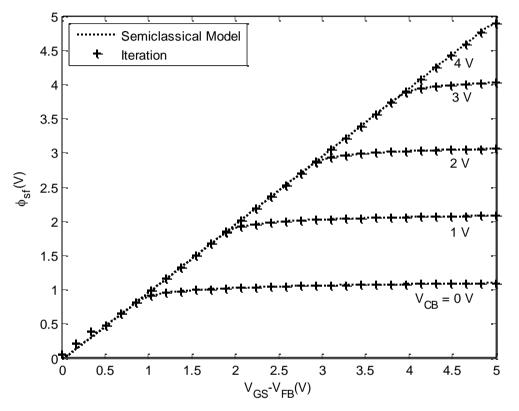

| Figure 4.4: For FD SOI, $\phi_{sf}$ versus gate voltage for different values of V <sub>CB</sub> . Here, $t_{soi} = 25$ nm              |

| and $t_{box} = 50 \text{ nm}$                                                                                                          |

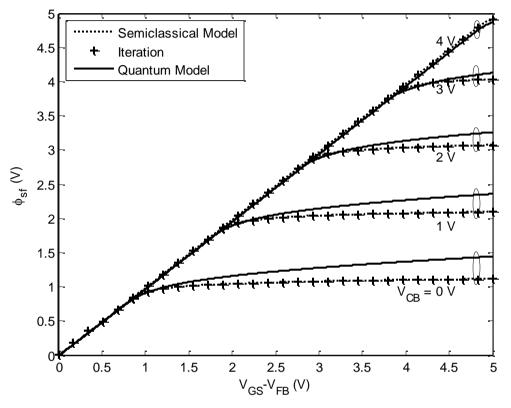

| Figure 4.5: For UTB SOI, $\phi_{sf}$ versus gate voltage for different values of V <sub>CB</sub> with QM                               |

| correction. Here, $t_{soi} = 8$ nm and $t_{box} = 50$ nm                                                                               |

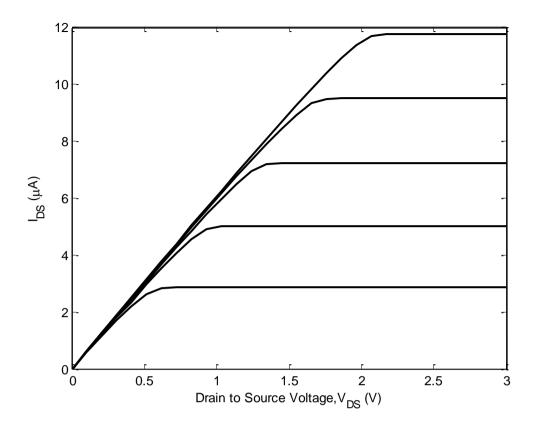

| Figure 4.6: For FD SOI, $V_{DS}$ versus $I_{DS}$ for different $V_{GS}$ . Here, $t_{soi} = 25$ nm and $t_{box} = 50$ nm.               |

|                                                                                                                                        |

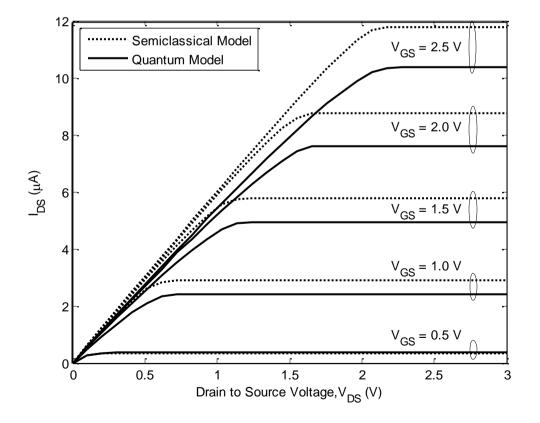

| Figure 4.7: For UTB SOI, V <sub>DS</sub> versus I <sub>DS</sub> for different V <sub>GS</sub> including QM correction of Drain         |

| current. Here, $t_{soi} = 8$ nm and $t_{box} = 50$ nm                                                                                  |

## List of Table

| Table 4.1: Parameter used in surface potential model verification       | 21 |

|-------------------------------------------------------------------------|----|

| Table 4.2: Percentage difference of Saturation Current                  | 27 |

| Table 4.3: Difference of V <sub>DS</sub> for obtaining transition point | 27 |

## Chapter 1 Introduction

The modern era of semiconductor electronics was guided by the invention of the bipolar junction transistor in 1948. In the 1960s MOS transistor technology has been introduced. Since then significant development of the MOS transistor technology has been done. Also dimensions of the transistors have decreased regularly. Currently bulk MOSFETs are reaching to the saturation of the scaling process. SOI MOSFET has been introduced in this process of the MOS transistor technology development. UTB SOI MOSFET is the successor of SOI MOSFET.

A SOI MOSFET is Silicon on Insulator (SOI) structure in which a semiconductor layer, like silicon is formed above an insulator layer. The SOI technology is introduced to overcome the limits of bulk or conventional Si MOSFETs. As MOSFETs goes to the nanometer region, SOI MOSFETs come with ultra thin body (UTB) where silicon film thickness is a few nanometers. As a result semi-classical mechanics does not exactly explain the performance of the UTB devices. In this situation Quantum Mechanical (QM) effects have started to play vital role in terms of performance of the UTB SOI MOSFET. Earlier QM effect was neglected because of the larger device size. Therefore it is necessary to include QM effects in transistor models.

In this work, we have analyzed QM effect over the front surface potential of the UTB SOI MOSFETs. Quantum mechanical effect on the drain current due to ultra thin body of SOI structure has been incorporated using a compact model. Usually compact models are the circuit models describing the terminal properties of the semiconductor devices that can be employed in circuit simulators. The properties of the devices in compact models are either defined by means of a simplified set of equations or by an equivalent circuit model. Results are presented and discussed.

#### 1.1 Background

Among the non-classic CMOS device concepts, an UTB SOI is one of the most promising approaches for future CMOS scaling to feature sizes below 50 nm. In contrast to other emerging device concepts, the UTB SOI technology combines a planar transistor configuration with a superior sub-threshold slope resulting from a thin Si-body thickness of 5–40 nm [1]. Together with reduced junction capacitances, high-k dielectrics, poly-SiGe gates or metal gates, these are attractive features for an energy-efficient CMOS logic operated at low supply voltages. With continual scaling of CMOS technology classical physics is inadequate to explain the behavior of a UTB SOI MOSFET. For modern day physics, where the MOS devices are down-scaled to the nanometer regime, QM effects have become an essential part [2].

To keep pace with the high density integration for SOI devices, it is necessary to reduce the silicon film thickness. This results in a narrow and deep potential well in the channel. Electrons get confined at the semiconductor-insulator interface and it becomes necessary to take QM effects into consideration. In the state-of-the-art devices due to increased vertical electrical field the carrier energy quantization has become significant. The energy quantization, threshold voltage ( $V_{th}$ ) shift and increase in surface potential are the results of the QM effect.

In order to predict the device performance and QM effect precisely various models have been developed, such as, numerical device simulation models, compact models etc. The requirements of numerical models, such as, rigorous computation and huge amount of memory, prevent them from being used for circuit simulation. Terminal properties of the devices have been described by the compact models by using simplified computation or by an equivalent circuit model. So these compact models are very popular for circuit simulation. QM effect can be predicted or modeled easily by compact models.

#### **1.2 Literature Review**

The generation of the idea of building MOSFET on an insulator was started at 1960s, and the idea was first applied in the thin-film transistor (TFT). At 1964 the first SOI transistors was implemented, which was a partially depleted device, fabricated on silicon-on-sapphire (SOS) substrates [3]. A variety of short-channel effects become significant as the scaling of CMOS technology continues to move into nanometre regime for high density and high performance integrated circuits, which limit the scaling of the device. In that situation, multi-gate MOSFET devices seem to be more attractive to control this limitation. Recently, excellent electrical characteristics have been shown by various transistors fabricated with a double gate structure. Moreover fully depleted (FD) SOI with ultra-thin body appeared to be the first device to replace the classical MOS architecture [4]. Compact models for SOI-MOSFETs have been developed by different research groups.

A number of analytical models have been suggested in the literature for modeling the current-voltage characteristics and the surface potential of SOI MOSFET, starting from the one-dimensional threshold voltage analytical model for thin film SOI MOSFETs, published by Lim and Fossum in 1983 [5]. Another model, which evaluates the surface potential for both partially depleted (PD) and FD SOI MOSFETs, using a single unified expression, proposed by Yu et al. [6] and the model is simplified one-dimensional analytical model. The model is free of iterations which is an advantage of this model [6] unlike the surface potential models given by Sleight and Rios [7] and by Bolouki et al. [8]. However, there are some weak points in the model given by Yu et al. [6] like, inability to correctly model the dependence of the front surface potential on the substrate voltage, self-inconsistent results due to misrepresentation of the operating modes of SOI devices, and ignoring the contribution of the inversion charge while expressing the back surface potential of the SOI film [9]. One of the advantages of this model [6] is that it provides a single formula for the

drain current which is obtained by smoothly connecting the analytic solutions for various operating regions.

Surface potential based MOSFET models have emerged as a better replacement to the threshold voltage based models. One of the main cause is surface potential based models provide consistent and accurate expressions for terminal currents and charges. These expressions are also valid in all regions of operations [10]–[17]. Many models based on surface potential approach have been developed for bulk MOSFETs which were implemented in different circuit simulators [11]–[14]. Surface potential based compact models have become popular for sub 100nm MOSFETs. However, modeling of FD SOI MOSFET is not same as MOSFETs because depletion charge in the substrate region is appear in FD SOI. FD SOI models like [6], [18], [19] do not consider the substrate depletion which were reported between 1989 to 2005 and because of this, these models cannot be used for FD SOI devices which have low substrate doping. Surface potential based FD SOI model of "Hiroshima University Semiconductor Technology Academic Research Centre IGFET model SOI (HiSIM-SOI)" [19] considers the substrate depletion explicitly.

The model of Francis et al. [20] has estimated the depletion charge by a constant value which is no longer valid in strong inversion regime for doped DG SOI transistors. As a result the model becomes less accurate in strong inversion. Some authors [21], [22], have presented a surface potential model for doped FD SOI MOSFETs. On the other hand, FD SOI model of HSIM [20] did not make any assumption, but the weak point of this model is that a single equation is provided to compute three different surface potentials (front, back and bulk surface potentials) that make the model inefficient. Unlike HSIM, recently published model [22] presented three equations for the three different surface potentials of the device.

To describe the transition characteristics between partially depleted and fully depleted operating regimes, a few compact models for SOI MOSFETs have been reported [7], [22], [23], [24]. The continuous compact model [7] is naturally continuous for the transition between the FD region and the PD region and uses an iterative procedure to calculate the front surface potential. In this model [7] the one-dimensional (1-D) Poisson equation was used to calculate the surface potential. But, in a large-scale simulation, the iteration could be a burden. The quasi-two-dimensional unified analytical front surface potential model [23] can explain both the FD region and the PD region. Although [23] is a fully analytic model, an iteration routine is required to obtain the critical front gate voltage defining the PD region and the FD region. The quasi-2-D nature of the model results in a surface potential in the strong inversion region and in the accumulation region that is different from the numerical solution of the 1-D Poisson equation. On the other hand BSIM SOI [24] is totally different from the surface potential models and uses an explicit threshold. The model most widely applied by industries is BSIM SOI based on the threshold-voltage concept [25]. By introducing an internal node this model [25] solves an unavoidable floating-body effect and the node potential is described analytically as a function of applied biases.

Circuit-simulation models for the SOI MOSFET have been developed to enable a reliable circuit design. Berkeley short-channel IGFET model-SOI (BSIM SOI) [26] and University of Florida SOI (UFSOI) [27], [28], are two major existing models which have been applied for the practical circuit simulation. Both models considered smooth transition between the partially depletion and the fully depletion condition during circuit operation.

There are some important features such as the parasitic bipolar effect and the generationrecombination current which have been included in those models [26]-[28]. These features are specific for the SOI-MOSFET. Both models have been developed as an extension of the bulk-MOSFET and suffer from nonconvergence problems in the circuit simulation [29], [30].

Now, it becomes important to have a closed-form single-equation solution of surface potential for different surfaces of the FD SOI device so that it can be used in circuit simulators. There is such solution available in the [22] that solves surface potentials at all surfaces of the FD SOI MOSFET explicitly considering the effect of substrate depletion. Here, by solving the 1-D Poisson equation a closed-form surface potential solution has been reported for all the surfaces of fully depleted SOI MOSFETs.

All the above models are based on semi-classical analysis. Several models have been proposed to incorporate QM effect in the surface potential of the bulk MOSFETs. Most exciting models incorporate QM correction through the band gap widening approach [31]. In 2010, a different QM correction approach to the semi-classical surface potential was proposed [32]. It directly adds the QM correction term to semi-classical surface potential. The model accounts for effect of wave function penetration within the proposed correction. This model proposed an explicit analytical term,  $\delta \phi_{sf}$ , which has been directly added to the semi-classical surface potential.  $\delta \phi_{sf}$  is the quantum mechanical correction to the semi-classical front surface potential.

#### 1.3 Objective

First of all our aim is to analyze the behavior of three surface potentials of the FD SOI MOSFETs, namely front oxide–silicon film surface  $\phi_{sf}$ , buried oxide–silicon film interface  $\phi_{sb}$ , and buried oxide–substrate interface  $\phi_{sbulk}$  due to the applied gate voltage. Also our objective is to analyze the drain current of FD SOI MOSFETs.

On the other hand in order to understand how the performance of UTB SOI MOSFET is affected by quantum mechanical effects, it is necessary to incorporate the QM correction on the semi-classical surface potential based compact model. The Karim and Haque model of [32] is a physically based model for QM corrections to the MOS surface potential. So our objective is to incorporate the QM effect into the surface potential of the UTB SOI MOSFET by using this model. We also want to investigate how QM effect influence the drain current of the UTB SOI MOSFET.

#### **1.4 Organization of the thesis**

In chapter 2 necessary reviews of SOI MOSFET and drain current model are discussed. In the following chapter 3, a brief explanation on QM effects and their theoretical derivation are given. Then later in chapter 3, basic approach of Karim and Haque model and mathematical derivations are explained. In chapter 4 and chapter 5, summary of results of the whole work, and conclusion, proposed work for the future are given respectively.

## Chapter 2 Surface Potential Based Model for FD SOI MOSFET

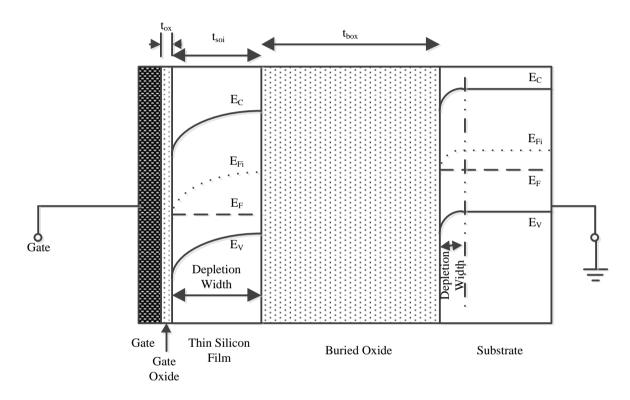

Surface potential is the total potential drop across the semiconductor region from the surface to a point in the bulk. In other word surface potential is the potential difference across the space charge layer. According to the SOI literatures there are three surfaces for the FD SOI MOSFET, these exist at front oxide–silicon film interface, buried oxide–silicon film interface, and buried oxide–substrate interface. The potentials at these Si/SiO<sub>2</sub> interfaces are functions of the terminal voltages as shown in Figure 2.1.

Figure 2.1: Energy Band Diagram for Depletion mode.

#### 2.1 Appreciation of the Surface Potential Based Model

In case of designing compact model the surface potential based model enhances the physical content and makes it more suitable for modeling advanced MOS devices. For getting consistent and accurate expressions for terminal currents and charges (which is valid in all regions of operations) surface potential based MOSFET models provide best results. Prior to surface potential based model the threshold voltage based models were used. As surface potential based models are suitable for simulating circuits with low power supply voltages and also allow physical modeling of the subthreshold region, which were the main drawbacks of the threshold-voltage-based models. Surface potential based models are better alternative to the threshold voltage based models [33]. Based on surface potential approach many models

have been developed for bulk MOSFETs and implemented in different circuit simulators. The same modeling approach has been extended to PDSOI MOSFET with a special consideration to effects, specific to PDSOI MOSFET, such as floating body and self-heating effects [34], [35]. Due to appearance of depletion charge in the substrate region, modeling of FD SOI MOSFET is quite different than bulk MOSFET. As a result, the surface potential based approach provides substantial advantage in the improvement of compact models. It also allows one to increase the physics content of the model. Furthermore, surface potential is a physical variable, which is a single expression for a particular surface.

#### 2.2 Introduction to Fully Depleted SOI structure

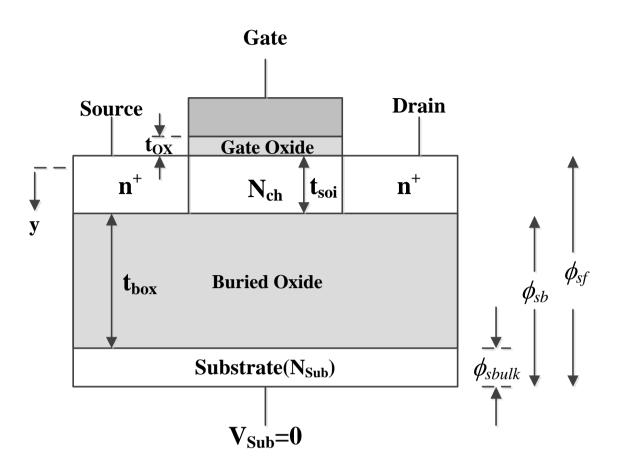

In case of an NMOS transistor, applying a positive gate voltage depletes the body of Ptype carriers and induces an N-type inversion channel on the surface of the body. For SOI structure a thin Silicon film is sandwiched between two oxide layers (i.e. Gate oxide and Buried oxide). As the film gets thinner the floating voltage becomes negligible. The two basic versions of single gate (SG) SOI MOSFET are the partially depleted (PD) SOI architecture and fully depleted (FD) SOI architecture. For PDSOI the silicon layer thickness is greater than the depletion layer, and for FDSOI the depth of the silicon layer thickness is equal to the thickness of the depletion region under the gate [36]. Figure 2.2 shows a fully depleted SOI MOSFET structure. The doping and the thickness for this type of SOI are varied in such a way that the SOI is fully depleted when the channel is inverted. As mentioned earlier the maximum depletion width for this type of SOI is equal to the thickness of the SOI film.

#### **2.3** Effect of substrate charge on the Surface Potential

In case of FD SOI the threshold voltage depends not only on the metal oxide work function, Fermi potential, and gate oxide fixed charge but also on the potential of the back channel. This back channel potential evolved from substrate charge. If the potential of the back channel is varied in such a way that it follows the potential of the front channel, then the threshold voltage will be smaller than that of the bulk MOSFET and the sub-threshold slope will be close to ideal value.

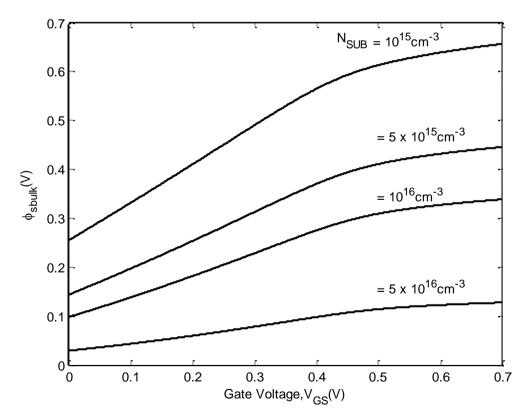

To further highlight the effect of substrate charge, plot of  $\phi_{sbulk}$  for different values of substrate doping is given in Figure 2.3. When the substrate doping is small (e.g.,  $10^{15}$  cm<sup>-3</sup>), then a large voltage drop appears across the substrate depletion region. With the increase of substrate doping, decrease of voltage drop across the substrate depletion region is observed.

Figure 2.2: Cross-sectional view of the FD SOI MOSFET.

Figure 2.3: Substrate surface potential  $\phi_{sbulk}$  versus gate voltage for different substrate doping.

#### 2.4 Analytical Solution of Surface Potential

Two assumptions are primarily taken for getting analytical solution of surface potentials (namely front oxide–silicon film surface  $\phi_{sf}$ , buried oxide–silicon film interface  $\phi_{sb}$ , and buried oxide–substrate interface  $\phi_{sbulk}$ ) for FD SOI MOSFET. These are: 1) The silicon film is always fully depleted and 2) The back silicon film surface is never inverted. By solving the 1-D Poisson equation in vertical direction and applying the boundary conditions at different surfaces three different equations are obtained [22].

In case of a FD SOI MOSFET as shown in Figure 2.2, the 1-D Poisson equation can be written as

$$\frac{\partial^2 \phi(\mathbf{y})}{\partial \mathbf{y}^2} = -\frac{\mathbf{q}}{\varepsilon_{\rm Si}} \left( \mathbf{p}(\mathbf{y}) - \mathbf{n}(\mathbf{y}) - \mathbf{N}_{\rm ch} \right)$$

(2.1)

where  $\phi(y)$  is the potential,  $\varepsilon_{si}$  is the permittivity of silicon, p(y) and n(y) are the hole and electron concentrations, respectively and N<sub>ch</sub> is the doping in the silicon layer [22]. By expanding the parentheses of (2.1) it can be further expressed as

$$\frac{\partial^2 \phi(\mathbf{y})}{\partial \mathbf{y}^2} = -\frac{q \mathbf{N}_{ch}}{\varepsilon_{Si}} \left\{ \left[ \exp\left(-\frac{\phi(\mathbf{y})}{\phi_t}\right) - 1 \right] - \exp\left(-\frac{2\phi_F + \mathbf{V}_{CB}}{\phi_t}\right) \left[ \exp\left(\frac{\phi(\mathbf{y})}{\phi_t}\right) - 1 \right] \right\}$$

(2.2)

where  $\phi_{\rm F}$  is the Fermi potential,  $\phi_{\rm t}$  is the thermal voltage, and V<sub>CB</sub> is the channel floating body potential, which varies from V<sub>SB</sub> at source to V<sub>SB</sub> + V<sub>DS</sub> at drain [22].

The boundary conditions need to be used in (2.2) are as follows:

1) Electric flux (displacement) at the front oxide/Si film interface is continuous (Gauss Law).

$$-\frac{\partial \phi(\mathbf{y})}{\partial \mathbf{y}}\Big|_{\phi(\mathbf{y})=\phi_{\mathrm{Sf}}} = \left(\frac{\mathbf{V}_{\mathrm{g}}-\phi_{\mathrm{sf}}}{\mathbf{t}_{\mathrm{ox}}}\right)\frac{\varepsilon_{\mathrm{ox}}}{\varepsilon_{\mathrm{Si}}}$$

(2.3)

where  $\epsilon_{ox}$  is the permittivity of the gate oxide,  $t_{ox}$  is the thickness of front gate oxide, and  $V_g = V_{GS} - V_{FB}$ , where  $V_{GS}$  is the gate-to-source bias voltage and  $V_{FB}$  is the flat-band voltage.

2) Electric flux at the buried oxide/Si film interface is continuous (Gauss Law).

$$-\frac{\partial \phi(\mathbf{y})}{\partial \mathbf{y}}\Big|_{\phi(\mathbf{y})=\phi_{\mathrm{sb}}} = \left(\frac{\phi_{\mathrm{sb}} - \phi_{\mathrm{sbulk}}}{t_{\mathrm{box}}}\right) \frac{\varepsilon_{\mathrm{ox}}}{\varepsilon_{\mathrm{Si}}}$$

(2.4)

where  $t_{box}$  is the thickness of buried oxide,  $\phi_{sb}$  is the surface potential at the buried oxide– silicon film interface, and  $\phi_{sbulk}$  is the surface potential at the buried oxide–substrate interface [22].

Substituting the two aforementioned boundary conditions the following equation is obtained.

$$\left(V_{g}-\phi_{sf}\right)^{2}-\frac{C_{box}^{2}}{C_{ox}^{2}}\left(\phi_{sbulk}-\phi_{sb}\right)^{2}=-\gamma^{2}\left\{\begin{array}{l}-\phi_{t}\left[\exp\left(-\frac{\phi_{sf}}{\phi_{t}}\right)-\exp\left(-\frac{\phi_{sb}}{\phi_{t}}\right)\right]-\left(\phi_{sf}-\phi_{sb}\right)\\-\exp\left(-\frac{2\phi_{F}+V_{CB}}{\phi_{t}}\right)\left(\phi_{t}\left[\exp\left(\frac{\phi_{sf}}{\phi_{t}}\right)-\exp\left(\frac{\phi_{sb}}{\phi_{t}}\right)\right]\right)\right\}\left(2.5\right)\right\}$$

where  $\gamma = \frac{\sqrt{2qN_{ch}\varepsilon_{si}}}{C_{ox}}$  and  $C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}}$  And  $C_{box} = \frac{\varepsilon_{box}}{t_{box}}$

Equation (2.5) has three unknowns namely  $\phi_{sf}$ ,  $\phi_{sb}$  and  $\phi_{sbulk}$ . It is known from mathematics that, to solve three unknowns three equations are needed. Therefore, two more equations are required to solve the unknowns and they can be obtained by solving the Poisson equation in the silicon film layer and the substrate region [22].

The Poisson equations for the substrate and silicon film are given by (2.6) and (2.7), respectively by assuming that inversion at the back silicon film surface and substrate never happen.

$$\frac{\partial^2 \phi(\mathbf{y})}{\partial \mathbf{y}^2} = -\frac{1}{\varepsilon_{\rm Si}} \left(-q \mathbf{N}_{\rm sub}\right)$$

(2.6)

$$\frac{\partial^2 \phi(\mathbf{y})}{\partial \mathbf{y}^2} = -\frac{1}{\varepsilon_{\rm Si}} \left(-q \mathbf{N}_{\rm ch}\right) \tag{2.7}$$

In case of writing (2.7) small voltage drop appearing across the front surface inversion charge layer has ignored, which simplifies the equation.

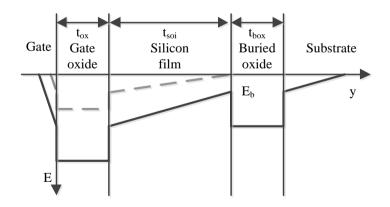

Figure 2.4: Electric field shape from the  $Si/SiO_2$  interface of the front gate oxide toward the substrate. The solid lines specify the electric field distribution for a given gate voltage. The dashed lines express the electric field when the silicon film is just depleted.

Solving Poisson's equation (2.6) and (2.7) following equations are obtained

$$\phi_{\rm sf} - \phi_{\rm sb} = \alpha + (\phi_{\rm sb} - \phi_{\rm sbulk}) \frac{C_{\rm box}}{C_{\rm soi}}$$

(2.8)

$$\phi_{\rm sb} = \phi_{\rm sbulk} + \gamma_{\rm bulk} \sqrt{\phi_{\rm sbulk}} \tag{2.9}$$

where

$$\gamma_{\text{bulk}} = \frac{\sqrt{2qN_{\text{sub}}\varepsilon_{\text{si}}}}{C_{\text{box}}}, \alpha = \frac{qN_{\text{ch}}t_{\text{soi}}^2}{2\varepsilon_{\text{si}}}, C_{\text{soi}} = \frac{\varepsilon_{\text{ox}}}{t_{\text{soi}}}, \text{ and } C_{\text{box}} = \frac{\varepsilon_{\text{ox}}}{t_{\text{box}}}$$

(2.5), (2.8) and (2.9) together describe the exact Poisson equation for an FD SOI MOSFET and are obtained without any approximation except the assumptions that the back silicon surface and the substrate region never go into inversion and that the device always remains in FD condition. By solving (2.5), (2.8) and (2.9) iteratively one can get the exact values of all three surface potential expressions [22].

Due to the nonlinear nature of (2.5), (2.8) and (2.9) a single closed-form solution for the surface potential cannot be obtained for the FD-SOI MOSFET as in the case of bulk MOSFETs. Therefore, separate solutions are first obtained in the weak and strong inversion regions, later; they are merged to get a single closed-form expression, as discussed in the following sections.

#### 2.4.1 SURFACE POTENTIAL SOLUTION:

To obtain the single closed-form solution for the surface potential, it is further assumed that the MOSFET does not operate in the accumulation region, which is a quite a valid assumption as the accumulation region is rarely used except in some specific applications. Hence, when  $\phi_{sf} > 3 \phi_t$ , (2.5) becomes

$$\frac{1}{\gamma^{2}} \left( \left( \mathbf{V}_{g} - \phi_{sf} \right)^{2} - \frac{\mathbf{C}_{box}^{2}}{\mathbf{C}_{ox}^{2}} \left( \phi_{sbulk} - \phi_{sb} \right)^{2} \right)$$

$$= \left( \phi_{sf} - \phi_{sb} \right) + \phi_{t} \left( 1 - \exp\left( -\frac{\phi_{sf} - \phi_{sb}}{\phi_{t}} \right) \right) \times \exp\left( \frac{-2\phi_{F} - \mathbf{V}_{CB} + \phi_{t}}{\phi_{t}} \right)$$

(2.10)

Finally, (2.8)–(2.10) are solved for the weak and strong inversion cases so that they can be unified with the help of smoothing functions as in the case of the bulk MOSFET.

#### 2.4.2 Weak inversion:

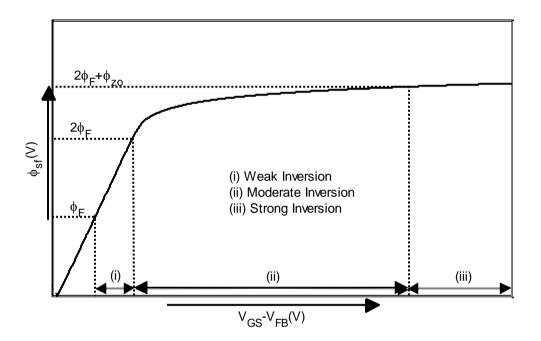

It is observed from Figure 2.5 that when  $\phi_F < \phi_{sf} < \phi_{2F}$  the MOSFET operates in weak inversion region. In this region, the small inversion charge appearing at the front silicon film surface can be neglected, as in the case of the bulk MOSFET. When the MOSFET is operating in weak inversion, the electric field variation in the vertical direction is shown in Figure 2.4, where the solid line denotes the electric field at a certain gate voltage V<sub>GS</sub>. In this case V<sub>C</sub> is the minimum voltage necessary to keep the device in the FD mode. In Figure 2.4,

the dotted line denotes the electric field variation in the vertical direction at  $V_C$ . At this voltage, the electric field at the buried oxide–silicon film interface becomes zero. Therefore,  $V_C$  can be written as

$$V_{\rm C} = \alpha + \frac{q N_{\rm Ch} t_{\rm soi}}{C_{\rm ox}}$$

(2.11)

Voltage  $V_g (=V_{GS} - V_{FB})$  is equivalent to the entire area under the electric field curve, shown in Figure 2.4.

Figure 2.5: Surface potential vs Gate voltage.

$E_b$  is the electric field at the buried oxide/substrate interface when the device has just reached FD.  $E_b$  can be written with respect to  $V_g$  as

$$E_{b} = -\frac{qN_{sub}}{C_{eff}} + \sqrt{\left(\frac{qN_{sub}}{C_{eff}}\right)^{2} + \frac{2qN_{sub}}{\varepsilon_{Si}}\left(V_{g} - V_{C}\right)}$$

(2.12)

where  $\frac{1}{C_{eff}} = \frac{1}{C_{ox}} + \frac{1}{C_{box}} + \frac{1}{C_{soi}}$  and  $N_{sub}$  is the substrate doping.

Finally, the value of  $E_b$  is used to obtain the expression of front surface potential in weak inversion as

$$\phi_{\rm sf,weak} = V_{\rm g} - \frac{\varepsilon_{\rm Si} t_{\rm ox}}{\varepsilon_{\rm ox}} \left( E_{\rm b} + \frac{q N_{\rm ch} t_{\rm soi}}{\varepsilon_{\rm Si}} \right)$$

(2.13)

where  $\phi_{\rm sf,weak}$  denote the front surface potential in the weak inversion region.

#### 2.4.3 Strong Inversion:

In the strong inversion region, (2.10) can be rearranged as (2.14).

$$\phi_{\rm sf,strong} = 2\phi_{\rm F} + V_{\rm CB} + \phi_{\rm t} \ln \left( \frac{\frac{1}{\gamma^2} \left( V_{\rm g} - \phi_{\rm sf,strong} \right)^2 - \frac{C_{\rm box}^2}{C_{\rm ox}^2} \left( \phi_{\rm sbulk,strong} - \phi_{\rm sb,strong} \right)^2 - \left( \phi_{\rm sf,strong} - \phi_{\rm sb,strong} \right)}{\phi_{\rm t} \left( 1 - e^{-\left( \frac{\phi_{\rm sf,strong} - \phi_{\rm sb,strong}}{\phi_{\rm t}} \right)} \right)} + 1 \right) (2.14)$$

where  $\phi_{sf,strong}$ ,  $\phi_{sb,strong}$ , and  $\phi_{bulk,strong}$  represent the front surface potential, back surface potential, and bulk surface potential in the strong inversion region, respectively. The value of  $\phi_{sb,strong}$  is given by (2.9) and  $\phi_{bulk,strong}$  can be acquired from (2.8) and (2.9) as

$$\phi_{\text{sbulk,strong}} = \left(-\beta + \sqrt{\beta^2 - \alpha + (\phi_{\text{sf,strong}})}\right)^2 \tag{2.15}$$

$$\left(1 + \frac{C_{\text{box}}}{2}\right)$$

where  $\beta = 0.5\gamma_{\text{bulk}} \left( 1 + \frac{C_{\text{box}}}{C_{\text{soi}}} \right)$

(2.14) is a nonlinear equation in terms of  $\phi_{sf,strong}$  and a direct solution of it cannot be obtained. Two approximations are suggested for (2.14) in the case of bulk and PDSOI MOSFET cases [34], [35]. The first approximation for the surface potential ( $\phi_{sf,strong}^1$ ) used in [35] is given as

$$\phi_{\rm sf,strong}^1 = 2\phi_{\rm F} + V_{\rm CB} \tag{2.16}$$

However, in [34], it is presented that the use of  $\phi_{sf,strong}^1$  results in a large error at the strong inversion region. In [34] it is also presented that a replacement of  $\phi_{sf,strong}$  by a value several times higher than  $2\phi_F + V_{CB}$  results in a good modeling at strong inversion but erroneous modeling at the moderate inversion region, which is critical for low-voltage designs. Therefore, this approximation was also rejected.

The second approximation  $\phi_{sf,strong}^2$  for the surface potential  $\phi_{sf,strong}$  recommended by [34] as following:

$$\phi_{\rm sf,strong}^2 = 2\phi_{\rm F} + V_{\rm CB} + \frac{\phi_{\rm sf,weak} - 2\phi_{\rm F} - V_{\rm CB}}{\sqrt{1 + \left(\frac{\phi_{\rm sf,weak} - 2\phi_{\rm F} - V_{\rm CB}}{\eta\phi_{\rm t}}\right)^2}}$$

(2.17)

where,  $\eta$  is a constant and its numerical value is between 4 and 6 to get a improved approximation for  $\phi_s$  in the case of bulk MOSFETs [34], [35]. Hence,  $\eta$  is taken as 6 for the range of doping and oxide thicknesses used in this paper. This approximation results in a

Department of Electrical and Electronic Engineering, East West University

)

more accurate final solution. Direct use of approximation (2.17) in (2.14) results in discontinuities at two points, which can cause serious problems in circuit simulators, and hence, a sharp increase in simulation time. Therefore, these discontinuities are removed by substituting  $2\phi_F + V_{CB}$  in (2.17) by a function *f*, which is continuous for all values of gate voltage changes from  $\phi_{sf,weak}$  at weak inversion to  $2\phi_F + V_{CB}$  at strong inversion [6], [34]

$$f = \frac{\phi_{sf,weak} + 2\phi_F + V_{CB} - \sqrt{(\phi_{sf,weak} - 2\phi_F - V_{CB})^2 + 4\delta_2^2}}{2}$$

(2.18)

where  $\delta_2$  is a fitting parameter and its value is taken as 0.1 [6], [34].

#### 2.4.4 Single piece model

To merge the two solutions of the front surface potential obtained from weak and strong inversion regions, a good smoothing function is needed. The criteria for smoothing function are: 1) it should be continuous and differentiable and 2) it should ensure that each of the approximations for the weak and strong inversions is reduced smoothly to insignificance outside of its respective region of validity. Since the nature of the front surface potentials in the weak and strong inversion conditions is similar to that of a PDSOI MOSFET, a well-known smoothing function is used to satisfy the two aforementioned requirements, which have been successfully used in the case of the PDSOI MOSFET [35]. The smoothing function is given as

$$\phi_{\rm sf} = \phi_{\rm sf,strong} - \phi_{\rm t} \ln \left( 1 + e^{\frac{\phi_{\rm sf,strong} - \phi_{\rm sf,weak}}{\phi_{\rm t}}} \right)$$

(2.19)

(2.19) relies on the statement that in strong inversion,  $\phi_{sf,strong} >> \phi_{sf,weak}$  and in the weak inversion  $\phi_{sf,strong} <<\phi_{sf,weak}$ . The continuity and infinite differentiability of the final  $\phi_{sf}$  is confirmed by the continuity and infinite differentiability of all the smoothing functions. After obtaining  $\phi_{sf}$ , the other two surface potentials  $\phi_{sb}$  and  $\phi_{sbulk}$  are obtained by using  $\phi_{sf}$  from (2.19) in (2.8) and (2.9). As there are three variables and values of these variables are obtained from numerical solution of (2.5), (2.8) and (2.9). In order to cross check whether the analytical calculated value from (2.8), (2.9) and (2.19) are matched with the numerical solution (2.5), (2.8) and (2.9) are needed.

#### 2.5 Surface Potential based drain current model

In this section the drain current model based on the surface potential is presented. In order to calculate the drain current Yu et al. model is used. In respect to calculation time consumption it is efficient one. However as mentioned in previous chapter that Yu et al. model has weakness in deriving surface potential so rather than using its surface potential derivation, here, [22] is used for surface potential derivation. The approximations made here

are similar to those made during  $\phi_{sf}$  analytical model derivation; moreover some other approximations are made here. These are (i) the ignoring current component due to the gradient of electron temperature, (ii) the gradual channel approximation and (iii) the charge sheet approximation. The drain current consists of drift and diffusion current components [35], [38]. By assuming that the current is constant along the channel and including series resistance effects [23], short-channel effects [38], self-heating effects [39], the polysilicon depletion effect [40], and the parasitic bipolar effect [41], drain current is given by

$$I_{DS} = \begin{cases} \frac{-b_1 - \sqrt{b_1^2 - 4a_1c_1}}{2a_1} & \text{for } R_D \neq R_S \\ -\frac{c_1}{b_1} & \text{for } R_D = R_S \end{cases}$$

(2.20)

where

$$\begin{aligned} a_{1} &= WC_{of} \,\mu_{n}^{0} \eta (R_{s} + R_{D}) \frac{R_{s} - R_{D}}{2} \\ b_{1} &= -WC_{of} \,\mu_{n}^{0} (R_{s} + R_{D}) \times \left[ V_{Gf} - V_{th} + \eta \phi_{t} - \frac{\eta R_{D}}{R_{s} + R_{D}} (\phi_{sfL} - \phi_{sf0}) \right] - L - \frac{\mu_{n}^{0}}{V_{sat}} (\phi_{sfL} - \phi_{sf0}) \\ c_{1} &= WC_{of} \,\mu_{n}^{0} \left[ V_{Gf} - V_{th} + \eta \phi_{t} - \frac{\eta}{2} (\phi_{sfL} - \phi_{sf0}) \right] (\phi_{sfL} - \phi_{sf0}) \end{aligned}$$

where Rs (Rd) is the source (drain) series resistance,  $V_{th}$  is the effective threshold voltage, L is the effective channel length including the channel length modulation, W is the channel width,  $\eta$  is a factor describing the bulk charge effects,  $\mu_n^0$  is the mobility at a given gate voltage and bulk voltage,  $\mu_0$  is the maximum low field mobility in the inversion layer, here we assume  $\mu_0 = \mu_n^0$ ,  $v_{sat}$  is carrier saturation velocity [23], [38] and [39]. The drain current I<sub>DS</sub> in (2.20) is expressed as a function of the surface potential at the source side  $\phi_{sf0}$  and at the drain side  $\phi_{sfL}$ . The front surface potential  $\phi_{sf}$  is obtained from the analytical surface potential model in section 2.4.

## **Chapter 3 Quantum Mechanical Effect**

Quantum mechanical (QM) effects are playing a significant role in SOI MOSFETs surface potential characteristics due to the ever shrinking feature size. Usually quantum mechanical effects are taking place for SOI MOSFETs in deep sub-micron region which means their channel length is in nanometer scale. Energy quantization in silicon film is a major quantum mechanical effect occurring in a SOI MOSFET at deep sub-micron region. So in this case, semi-classical models are inadequate to model the device preciously, which will lead to erroneous and misleading predictions of critical device structure and electrical behavior parameters such as the physical oxide thickness, threshold voltage, drive current, surface potential, gate capacitance and sub-threshold swing.

## **3.1** Energy quantization in the Silicon film due to quantum mechanical effects

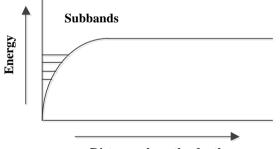

As the dimensions of the devices approach deep submicron and nanometer regions, the classical movement of the charge carriers is greatly affected by the non-classical behavior of electrons in the SOI MOSFETs. The scaling down of SOI MOSFETs is accomplished by the result of thinner oxide and smaller device size which leads to the improvement of electric field at different interfaces. For very high electric fields in the silicon/silicon oxide interfaces, the potential at the interfaces becomes steep. So a potential well is formed by the oxide barrier and the silicon conduction band under inversion condition. The carriers are confined in this narrow potential well. Because of the confinement of the carriers, inversion layer electrons must be treated quantum mechanically as a two dimensional electron gas. Due to this confinement, the electron energies are quantized and hence the electrons occupy only discrete energy levels. This results in the electrons residing in some discrete energy levels as shown in Figure 3.1 which are above the classical energy level.

Distance along the depth

Figure 3.1: Discrete energy levels due to quantization (in the substrate).

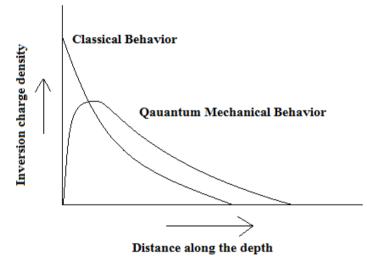

Due to the narrow potential well the motion of the carriers of the surface channel is quantized in the direction perpendicular to the interface; consequently the carrier (probability) density is at maximum inside the well and not at the boundaries, as shown in Figure 3.2. In addition, the minimum energy for the electrons in the conduction energy

subbands increases with the electron concentration. This effect reduces the current drive of the device and is not predicted by classical simulators [42].Therefore, the operation of deeply scaled SOI transistors cannot be accurately described by semi-classical physics, and accurate calculation of the inversion charge requires introducing concepts derived from quantum mechanics (QM).

Figure 3.2: Electron concentration distribution in the silicon substrate in classical and quantum mechanical cases.

#### **3.1.1 Threshold Voltage shift**

It is found that, due to quantum confinement of carriers in a thin silicon layer, the minimum energy for electrons in the conduction band increases when the thickness of the silicon film is reduced. As a result, the threshold voltage increases as the film thickness is reduced. Furthermore, the minimum energy for the electrons in the conduction energy sub bands increases with the electron concentration, which dynamically increases the threshold voltage [42]. The carrier confinement in very narrow potential well is governed by the wave functions and energy levels of the various sub bands. As the film becomes thinner than 10 nm, the energy levels and their separation increases, making them harder to populate, so the threshold voltage increases.

#### **3.1.2** Shift in surface potential

According to the semi-classical model at strong inversion surface band bending will be almost fixed. At this situation slight increase in surface potential results in a large build up of electron density at the surface. Devices with gate oxide in nanometer range results in high electric field so the surface band bending from the quantum mechanical model is considerably larger than that from the classical model. This is because the 2-D carrier distribution of the sub bands and discrete energy levels lead to reduced charge density compared to semi-classical calculation. As a result an additional band bending is required for an increased charge density. So this results to increase in surface potential. Therefore, the operation of deeply scaled SOI transistors cannot be accurately described by semi-classical physics, accurate calculation of the inversion charge requires introducing concepts derived from quantum mechanics (QM).

#### 3.2 Quantum Mechanical Correction to the Surface Potential of Nanoscale FD SOI MOSFETs

Different techniques and models have been proposed over the years to incorporate the quantum mechanical effects for MOS transistors, which can be used for SOI transistors as well. Such as band-gap widening model which indirectly includes quantum mechanical (QM) correction [31]. In this model, the proposed QM corrections are either derived from triangular well approximation or variational technique [2]. The physics of both approaches are dependable but none of the techniques are quantitatively correct. A physically based explicit analytical model for the QM correction the surface potential of nanoscale MOS devices was proposed in [32]. Recent study showed this model provides a more accurate QM correction method than the previous ones over a large range of device parameters.

#### 3.2.1 Basic approach of the Karim and Haque QM model

The Karim and Haque QM correction model to the semi-classical surface potential  $(\phi_{sf})$ , is valid for both MOS and SOI devices. This model directly adds the QM correction term to the semi-classical  $\phi_{sf}$ , instead of applying indirect band-gap widening approach.

As the Karim and Haque QM model dictated according to the semi-classical charge sheet model, the inversion carriers are treated as a sheet charge at the Si-film–front-oxide interface of SOI MOSFET. Under the inversion bias due to the QM effect quantization of the energies of the mobile charge carriers occurred which is discussed in section 3.1. According to the QM charge sheet model, the effect of QM shifts the sheet charge corresponding to the quantized charge carriers into front Si of UTB SOI MOSFET by an amount. The amount of shift is called  $Z_{av}$  here, which is the average distance of charges from the Si-film–front-oxide interface considering the QM effect. This is the primary reason of increase in front surface potential ( $\phi_{sf}$ ) due to QM effect. Most existing surface-potential-based models use the bandgap widening approach to incorporate QM correction to the semi-classical  $\phi_{sf}$ . On the other hand in this model they are using the physics of the QM charge sheet model and propose the correction to the surface potential due to the QM effect as

$$\delta\phi_{sf} = -\frac{Q_{inv}Z_{av}}{\varepsilon_0\varepsilon_{Si}} \tag{3.1}$$

where  $Q_{inv}$  is the inversion layer charge density.

The surface potential  $\phi_{sf[am]}$  including the QM effect is expressed as

$$\phi_{\rm sf[qm]} = \phi_{\rm sf[sc]} + \delta \phi_{\rm sf} \tag{3.2}$$

Here,  $\phi_{sf[sc]}$  is the semi-classical front surface potential neglecting QM effects, which can be estimated from the equations of [44] by considering the effect of substrate charge explicitly. For calculating the  $\phi_{sf[qm]}$  we only consider front surface potential and neglect other surface potential of SOI MOSFET. We only investigate the QM effect on the drain current of the UTB SOI MOSFET. In order to obtain the drain current from surface potential we use (2.20) where only front surface potential is needed. So, we neglect other surface potential of UTB SOI MOSFET for incorporating the QM effect on surface potential and drain current.

The energies of the quantized states are proportional to  $F_{ox}^{2/3}$  according to the Airy function approximation, where  $F_{ox}$  is the oxide electric field. For the state of-the-art nanoscale MOSFETs, the two-third power law which is stated above is not accurate. Though, this approximation provides a simple analytical expression for QM correction. However, it has been shown that the quantized energies of the quasi-bound states follow a power–law relationship, as functions of  $F_{ox}$ , which is different from the two-third power law, as predicted by the Airy function approximation, even when the wave function penetration effect into the gate dielectric is considered. The energy of the lowest quasi-bound state  $E_1$  is measured from the respective band edge.  $E_1$  Expressed in [46] is as:

$$\mathbf{E}_{1} = \zeta_{1} \left( \frac{\left| \mathbf{F}_{ox} \right| \mathbf{cm}}{\mathbf{MV}} \right)^{\lambda}$$

(3.3)

Here,  $\zeta_1 = 77 \text{meV}$  and  $\lambda = 0.61$  for electrons, and  $\zeta_1 = 88 \text{meV}$  and  $\lambda = 0.64$  for holes incorporating the wave function penetration effect. The penetration of the wave function into the oxide increases with shrinking gate oxide thickness and increasing substrate doping concentration [47]. Precise evaluation of the quantized eigen energy levels in the semiconductor region depends on the amount of this wave function penetration into the oxide region. The wave function has to be taken into account.  $Z_{av}$  is reduced when wave function penetration effect is taken into account for a given semiconductor charge density. As a result of reduction in  $Z_{av}$  magnitude of the surface potential is also being reduced.

$Z_{av}$  Can be written as:

$$Z_{av} = \frac{E_1}{qF_s}$$

(3.4)

where F<sub>s</sub> is the electric field at the gate oxide, Si film interface of UTB SOI.

#### 3.2.2 Derivation of a mathematical expression of the proposed QM model

In the inversion region inversion charge density  $Q_{inv} = Q_s - Q_b$  which can be expressed as:

$$Q_{inv} = -C_{ox} \left( V_g - V_{FB} - \phi_{sf[qm]} \right) - Q_b$$

(3.5)

where  $C_{ox} = (\varepsilon_0 \varepsilon_{ox} / T_{ox})$  is the oxide capacitance per unit area,  $V_{FB}$  is the flat-band voltage,  $Q_b = \mp \gamma C_{ox} \sqrt{|\phi_{sf}[qm]|}$  Is the depletion charge density, and  $\gamma = \frac{\sqrt{2qN_{ch}\varepsilon_0\varepsilon_{si}}}{C_{ox}}$  is the body factor. Here, the (-) sign is for n-MOS devices, and the (+) sign for p-MOS devices. An implicit equation for  $\delta \phi_{sf}$  can be obtained by substituting (3.5) into (3.1) and using (3.2). This implicit equation can be solved iteratively. For computational efficiency the numerical solution of the implicit equation is not smart.

It has numerically been verified that  $\delta \phi_{sf}$  shows satisfactory convergence after the first two iterations. An explicit analytical expression for  $\delta \phi_{sf}$  can be derived considering only the first two iterations, which are expressed as:

$$\delta \phi_{\rm sf} = \frac{C_{\rm ox} \left[ V_{\rm g} - V_{\rm fb} - \left( \phi_{\rm sf[sc]} + \delta \phi_{\rm sf}^{1} \pm \gamma \sqrt{\left| \phi_{\rm sf[sc]} + \delta \phi_{\rm sf}^{1} \right|} \right) \right] E_{1}^{1}}{q \varepsilon_{\rm o} \varepsilon_{\rm ox} F_{\rm ox}^{\rm l}}$$

(3.6)

And  $\delta \phi^{1}_{s}$ , the first order solution is

$$\delta \phi_{\rm sf}^{1} = \frac{C_{\rm ox} \left[ V_{\rm g} - V_{\rm fb} - \left( \phi_{\rm sf[sc]} \pm \gamma \sqrt{|\phi_{\rm sf[sc]}|} \right) \right] E_{1}^{0}}{q \varepsilon_{\rm o} \varepsilon_{\rm ox} F_{\rm ox}^{0}}$$

(3.7)

Here, the (+) signs are for n-MOS devices, and the (-) signs are for p-MOS devices.  $E_1^0$  and  $F_{ox}^0$  are the zeroth-order terms, and  $E_1^1$  and  $F_{ox}^1$  are the first-order terms respectively. These are given by:

$$\mathbf{E}_{1}^{0} = \zeta_{1} \left( \frac{\left| \mathbf{F}_{ox}^{0} \right| \mathbf{cm}}{\mathbf{MV}} \right)^{\lambda}$$

(3.8)

$$\mathbf{E}_{1}^{1} = \zeta_{1} \left( \frac{\left| \mathbf{F}_{ox}^{1} \right| \mathbf{cm}}{\mathbf{MV}} \right)^{\lambda}$$

(3.9)

$$F_{ox}^{0} = \frac{C_{ox} \left( V_{g} - V_{fb} - \phi_{sf[sc]} \right)}{\varepsilon_{0} \varepsilon_{ox}}$$

(3.10)

$$F_{ox}^{1} = \frac{C_{ox} \left[ V_{g} - V_{fb} - \left( \phi_{sf[sc]} + \delta \phi_{sf}^{1} \right) \right]}{\varepsilon_{0} \varepsilon_{ox}}$$

(3.11)

19

The main result which can be added to the semi-classical surface potential to attain QM corrected result is  $\delta\phi_{sf}$  here.

From (3.6) and (3.7) it can be realized that surface potential with QM effect leads to diverging derivative with respect to the gate voltage at flat-band  $V_{FB}$ . It has been founded by using numerical verification that  $\delta \phi_{sf}$  is negligible around the flat-band [32]. The problem of diverging derivative has been overcome exploiting this observation. It has done as follows:

$$\phi_{sf[qm]} = \phi_{sf[sc]}, V_{tr1} \le V_{gs} - V_{FB} \le V_{tr2}$$

=  $\phi_{sf[sc]} + \delta \phi_{sf}$  otherwise (3.12)

Here,  $V_{tr1}$  and  $V_{tr2}$  are two transition voltages such that  $V_{tr1} < 0$  and  $V_{tr2} > 0$ . Choices for  $V_{tr1} = -0.001$  V and  $V_{tr2} = 0.2$  V for n-MOS and for p-MOS devices,  $V_{tr1} = -0.15$  V and  $V_{tr2} = 0.001$  V that work well for all cases.

## Chapter 4 Results and Discussion

In our work we have analyzed the surface potentials for all the three surfaces (gate oxide–silicon film interface, silicon-film–buried oxide interface, and buried oxide–substrate interface) of fully depleted silicon-on-insulator (SOI) MOSFETs by considering the effect of substrate charge explicitly and hence obtain I-V characteristics based on the surface potential based compact model. As already mentioned in the previous discussions due to ultra thin body of the UTB SOI MOSFET the semi-classical models become inadequate. So, the Quantum mechanical effects need to be considered. So, finally we include quantum mechanical effect in surface potential to analyze the impact of quantum mechanical correction to the surface potential based compact model on the drain current of UTB SOI MOSFET.

#### 4.1 Surface Potential

For calculating surface potential we choose [22] where it is assumed that no inversion takes place at the back surface and the silicon layer is fully depleted. Most of the parameter values are also taken from [22]. Values of all the parameters used in our model are given in the following table.

| Parameter                                               | Value                              |

|---------------------------------------------------------|------------------------------------|

| Dielectric constant of Silicon                          | 11.7                               |

| Dielectric constant of Silicon-di-oxide                 | 3.9                                |

| Front oxide thickness, tox                              | 3 nm                               |

| Silicon film thickness, t <sub>soi</sub>                | 8 nm, 25 nm                        |

| Buried oxide thickness, t <sub>box</sub>                | 16 nm, 50 nm                       |

| Silicon Film doping, N <sub>ch</sub>                    | $10^{17} \mathrm{cm}^{-3}$         |

| Substrate doping, N <sub>sub</sub>                      | $10^{15} \mathrm{cm}^{-3}$         |

| Silicon Intrinsic carrier concentration, n <sub>i</sub> | $1 \times 10^{10} \text{ cm}^{-3}$ |

| Room Temperature                                        | 300 K                              |

| Flat band voltage, V <sub>FB</sub>                      | 0.5 V                              |

| Substrate voltage, V <sub>sub</sub>                     | 0 V                                |

Table 4.1: Parameter used in surface potential model verification

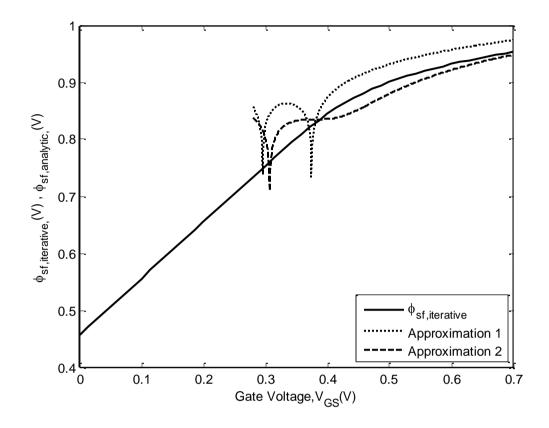

For calculating surface potentials for all three surfaces first we calculate  $\phi_{sf}$ . In order to do so first we solve (2.5), (2.8), and (2.9) iteratively and plot the exact solution of  $\phi_{sf}$  then the analytical strong inversion surface potential solution obtained from (2.14), (2.16), and (2.17). By using (2.16) and (2.17) in the right side of (2.14) we obtain Approximations 1 and

2 respectively which are basically two solution of  $\phi_{sf,strong}$  then we compare it with the iterative solution of  $\phi_{sf}$ .

Figure 4.1: For FD SOI, comparison of  $\phi_{sf}$  obtained iteratively and analytically. Here,  $t_{soi} = 25$  nm and  $t_{box} = 50$  nm.

Figure 4.1 shows a comparison between the exact solution of the front surface potential which we get from iteration and the analytical strong inversion surface potential solution. From above figure we observe that Approximation 2 is closer to the exact solution.

In Figure 4.2 elimination of the discontinuities is presented. The figure displays the plots of  $\phi_{sf,weak}$ ,  $\phi_{sf,strong}$ , obtained from (2.14) and (2.16)–(2.18), and the iterative solution of the surface potential, acquired from (2.5), (2.8), (2.9). In both the weak and strong inversion regions good match is achieved. Moreover, in the strong inversion solution, no discontinuity is observed.

In order to obtain analytical surface potentials  $\phi_{sf}$ ,  $\phi_{sb}$ , and  $\phi_{sbulk}$  we used (2.19), (2.14), and (2.15). Afterward we compare them with numerically solved surface potentials which are obtained by using (2.6), (2.14), and (2.15).

Figure 4.2: For FD SOI,  $\phi_{sf,weak}$ ,  $\phi_{sf,strong}$ , and  $\phi_{sf,iterative}$  versus gate voltage. Here,  $t_{soi} = 25$  nm and  $t_{box} = 50$  nm.

Figure 4.3: For FD SOI, three surface potentials  $\phi_{sf}$ ,  $\phi_{sb}$ , and  $\phi_{sbulk}$  versus gate voltage. Here,  $t_{soi} = 25$  nm and  $t_{box} = 50$  nm.

The variation of surface potentials  $\phi_{sf}$ ,  $\phi_{sb}$ , and  $\phi_{sbulk}$  versus the gate voltage is observed in Figure 4.3. To clearly demonstrate the effect of substrate depletion charge on the front surface potential the substrate doping is selected quite low (10<sup>15</sup> cm<sup>-3</sup>). A large potential drop appears across the substrate depletion region, when the substrate doping is low, which changes the channel inversion charge density significantly. Figure 4.3 undoubtedly demonstrates a large drop across the substrate region given by  $\phi_{sbulk}$ . The surface potentials from the analytical solution are in close proximity with the iterative results.

Figure 4.4: For FD SOI,  $\phi_{sf}$  versus gate voltage for different values of V<sub>CB</sub>. Here,  $t_{soi} = 25$  nm and  $t_{box} = 50$  nm.

In order to obtain semi-classical front surface potential  $\phi_{sf}$  analytically for FD SOI MOSFET we use (2.19) and then we compare  $\phi_{sf}$  with numerically solved surface potentials which are obtained by solving (2.6), (2.14), and (2.15) iteratively. The result is shown in Figure 4.4.

To obtain quantum correction of  $\phi_{sf}$  of UTB SOI we use (3.12). For obtaining  $\phi_{sf[sc]}$  we used the same approach as used for obtaining  $\phi_{sf}$  of FD SOI MOSFET. However for UTB SOI we take  $t_{soi} = 8$  nm. In this case we found a maximum relative error of 0.6% between the analytical solution of three surface potentials and iterative solution of exact Poisson equation. The relative error is calculated using the following formula

Relative error =

$$\frac{\text{Analytical solution} - \text{Iterative solution}}{\text{Iterative solution}} \times 100\%$$

Figure 4.5 shows variation of  $\phi_{sf}$  with gate voltage for different values of the channel floating voltage V<sub>CB</sub>. We notice that the surface potential varies linearly in the weak inversion region and then saturates at high values of gate voltages similar to that observed in the case of bulk MOSFETs. The simulation results are in close proximity with the results obtained from the iterative solution of the Poisson equation.

Figure 4.5: For UTB SOI,  $\phi_{sf}$  versus gate voltage for different values of V<sub>CB</sub> with QM correction. Here,  $t_{soi} = 8$  nm and  $t_{box} = 50$  nm.

As we discussed in the section 3.1.2, including quantum mechanical effect in surface potential increases surface potential. The result is shown in the Figure 4.5. From Figure 4.5 it is also observed that for higher value of  $V_{CB}$  we get almost same front surface potential from semi-classical and quantum mechanical model in this figure. The reason of this is as we increase  $V_{CB}$ , weak inversion is extended and it still doesn't reach the strong inversion. As discussed in the section 3.1.2 lack of charge carrier density in the Silicon film is the reason of increase in front surface potential, so here  $\phi_{sf}$  is not increased so much.

#### 4.2 Drain Current

For FD SOI MOSFET we calculate drain current using (2.20) which need front surface potential  $\phi_{sf}$  for its calculation. The result is given in Figure 4.6.

In case of UTB SOI MOSFET we calculate the drain current for both semi-classical and quantum mechanical model using (2.20) which require front surface potential  $\phi_{sf}$  for its calculation.

Figure 4.6: For FD SOI,  $V_{DS}$  versus  $I_{DS}$  for different  $V_{GS}$ . Here,  $t_{soi} = 25$  nm and  $t_{box} = 50$  nm.

Figure 4.7: For UTB SOI,  $V_{DS}$  versus  $I_{DS}$  for different  $V_{GS}$  including QM correction of Drain current. Here,  $t_{soi} = 8$  nm and  $t_{box} = 50$  nm.

For semi-classical model  $\phi_{sf}$  is obtained from (2.19) and for quantum mechanical model  $\phi_{sf}$  is obtained from (3.12). Result is given in Figure 4.7.

| $V_{GS}(V)$ | I <sub>DS</sub> (sat) (SC) μA | I <sub>DS</sub> (sat) (QM) µA | Percentage difference |

|-------------|-------------------------------|-------------------------------|-----------------------|

| 2.5         | 11.78                         | 10.36                         | 12.05                 |

| 2           | 8.76                          | 7.61                          | 13.13                 |

| 1.5         | 5.78                          | 4.93                          | 14.71                 |

| 1           | 2.88                          | 2.41                          | 16.32                 |

| 0.5         | 0.35                          | 0.36                          | 2.86                  |

Table 4.2: Percentage difference of Saturation Current

|  | Table 4.3: Difference | of V <sub>DS</sub> | for o | btaining | transition | point |

|--|-----------------------|--------------------|-------|----------|------------|-------|

|--|-----------------------|--------------------|-------|----------|------------|-------|

| $V_{GS}(V)$ | V <sub>DS</sub> (tran) (SC) V | V <sub>DS</sub> (tran) (QM) V | Difference (V) |

|-------------|-------------------------------|-------------------------------|----------------|

| 2.5         | 2.27                          | 2.27                          | 0.00           |

| 2           | 1.79                          | 1.77                          | 0.02           |

| 1.5         | 1.31                          | 1.31                          | 0.00           |

| 1           | 0.81                          | 0.82                          | 0.01           |

| 0.5         | 0.39                          | 0.38                          | 0.01           |

In Figure 4.7 we observe semi-classical analytical compact model, and quantum corrected model of drain current vs.  $V_{DS}$  for various  $V_{GS}$ . As we used Karim and Haque model [32] for quantum mechanical correction and in Karim and Haque model it is mentioned that it include quantum mechanical effect by considering wave function penetration through the gate oxide, so here we see that drain current obtained from quantum model is less than the drain current obtained from semi-classical model. At the same gate voltage ( $V_{GS}$ ) inversion carrier density is lower for the QM effect, as a result QM corrected drain current is lower than semi-classical model.

From Table 4.2 it is found that, with the change of  $V_{GS}$  percentage difference between semi-classical and QM corrected drain current is almost constant, but at  $V_{GS} = 0.5V$  this assumption is not correct because here threshold voltage,  $V_{th} = 0.346V$ , so device does not reach strong inversion at this point and two current is almost the same. In Table 4.3 we observe slight change in transition voltage between quantum model and Semi-classical model for different value of  $V_{GS}$ . For a fixed  $V_{GS}$  transition voltage is the voltage between the linear region and the saturation region of the  $I_{DS}$ - $V_{DS}$  characteristics.

#### 5.1 Conclusion

In our work we have studied the impact of Quantum Mechanical correction on the drain current of UTB SOI MOSFET. We included the quantum mechanical effect into front surface potential of UTB SOI MOSFET by using Karim and Haque model [32]. Surface potential based compact model of FD SOI MOSFET is used to obtain semi-classical  $\phi_{sf}$  for UTB SOI MOSFET.

Prior to studying the impact of Quantum Mechanical Effect on surface potential we have studied a closed-form surface potential solution for all the three surfaces of the FD SOI MOSFET. The effect of substrate charge is considered explicitly. We observed that if the doping density of the substrate is varied then back surface potential for SOI structure also varied. Closed form of surface potential solution is derived from the solution of 1-D Poisson equation.

We observed that the insertion of QM correction into the front surface potential ( $\phi_{sf}$ ) of UTB SOI MOSFET increases  $\phi_{sf}$ . QM correction results decrease of drain current in strong inversion region of the UTB SOI MOSFET. In comparison with semi-classical model the increase of  $\phi_{sf}$  and decrease of drain current is observed.

In section 3.1.2, it is discussed that including quantum mechanical effect in surface potential will increase surface potential. The lack of charge carrier density in the Silicon film is the reason of increase in front surface potential. The drain current obtained from quantum model is less than the drain current obtained from semi-classical model.

#### 5.2 Future Work

Further extension of our work can be done more accurately and comprehensively. As the channel length L is reduced to increase both the operation speed and the number of components per chip, short-channel effects arise such as drain-induced barrier lowering, velocity saturation, and impact ionization. These short channel effects can be included to make this model more realistic. Our work is based on 3 nm gate oxide. And for thinner gate oxides, gate leakage current is significant which can be analyzed. Here we use constant mobility, but mobility depends on several factors which can be included in future work. Moreover, removal of excess heat generated within the SOI devices is less efficient than in bulk devices, which may result in a substantial increase in device operating temperature and the phenomenon is called self heating effect. Self heating is due to the thermal isolation of transistors from the substrate by the buried insulator. In future one can incorporate the thermal variation of the device. One can also analyze the effect of parasitic capacitance over this model. Besides, comparison between other models can be made to have a better idea of the device performance. With the decreasing length of the channel, ballistic Quantum

transport is playing a vital role. So, further improvement of this model should do by incorporating the ballistic transport effect.

## Matlab code for obtaining figure 2.3, figure 2.5 and figures in Result section :

```

% Matlab 10 (version 10) is used in writing and simulation of the code

function utbsoi

clc

clear all

q=1.602e-19; % Charge magnitude of electron (C)

eta=6; % A factor describing the bulk charge effects

delta2=0.1; % A fitting parameter

% All units are converted into cm.cm^2.cm^3.

esi=11.7*8.854e-14; % Dielectric constant of Silicon [F/cm]

eox=3.9*8.854e-14; % Dielectric constant of Silicon Dioxide [F/cm]

tox=3e-7; % Front oxide thickness [cm]

tsoi=8e-7; % Silicon film thickness [cm]

tbox=50e-7; % Buried oxide thickness [cm]

Cox=eox/tox; % Front oxide capacitance per unit area [F/cm^2]

Csoi=esi/tsoi; % Silicon film capacitance per unit area [F/cm^2]

Cbox=eox/tbox; % Buried oxide capacitance per unit area [F/cm^2]

Ceff=1/((1/Cox) + (1/Cbox) + (1/Csoi));

% Series capacitance per unit area [F/cm^2]

Nch=1e17; % Silicon film doping(in which channel formed) [cm^-3]

Nsub=1e15; % Substrated doping (or impurity in bottom silicon part) [cm^-3]

W=10e-4; % Silicon film width [cm]

L=0.1e-4; % Silicon film length [cm]

mu n=1350; % mobility of electron for Silicon,Si at temperature=300K

Rs=(80000e-3)/W; % source series resistance

v sat=1e7; % Carrier saturation velocity

phi t=0.0259; % Thermal voltage at 300k [V]

ni=1e10; % Silicon intrinsic carrier concentration per unit area [cm^-3]

phi f=phi t*log(Nch/ni); % Fermi potential [V]

VFB=-0.5; % Flat band voltage mentioned [V]

Vgs=linspace(0,0.7,1000); % This Vgs for analytical model plot. One should

%take a lot of point otherwise for fig(1) shape does not appear correctly.

Vg=Vgs-VFB; % For analytical model

Vcb=0; % Channel floating voltage

%phi_sf_strong_calc where Vcb=0,Nsub=1e15

Vgsi=linspace(0,0.7,50); % This Vgsi for iteration plot. Here few points

%are taken for faster computation. If one wants to find the relative error

%then Vgsi must be equal to Vgs.

Vgi=Vgsi-VFB; % This Vgi for iteration

[phi_sf_iter,phi_sb_iter,phi_sbulk_iter]=phi_calc_iter(Vgi,Vcb);% function

% derived in the function derivition section

[phi sf strong, phi sb strong, phi sbulk strong, phi sf strong1, ...

phi_sb_strong1,phi_sbulk_strong1,phi_sf_strong2,phi_sb_strong2,...

phi sbulk strong2]=phi strong calc(Vg,Vcb);% function derived in the

%function derivition section

figure(1)

plot(Vgsi,abs(phi sf iter),'k','LineWidth',2)

hold on

plot(Vgs(Vgs>0.28), abs(phi sf strong1(Vgs>0.28)), ':k', 'LineWidth', 2)

```

```

hold on

plot(Vgs(Vgs>0.28), abs(phi sf strong2(Vgs>0.28)), '--k', 'LineWidth', 2)

hold on

xlabel('Gate Voltage,V G S (V)')

% phi sf weak and phi sf strong calculation and comparing them with phi sf

% iteration here Nsub=1e15 & Vcb not used

[phi sf weak]=phi weak calc(Vg);

% function derived in the function derivition section

figure(2)

plot(Vgsi,abs(phi sf iter), 'k', 'LineWidth',2)

hold on

plot(Vgs,abs(phi sf strong),':k','LineWidth',2)

hold on

plot(Vgs,abs(phi sf weak),'--k','LineWidth',2)

% Three surface potentials analytical model and numerical model comparison

% section phi_sf_calc where Vcb=0,Nsub=1e15

[phi sf,phi sb,phi sbulk]=phi calc(); % function derived in the function derivition section

figure(3)

plot(Vgs,phi sf,'k','LineWidth',2)

hold on

% otherwise it can be mentioned below

hold on

plot(Vgs,phi sb,'k','LineWidth',2)

hold on

plot(Vgs,phi sbulk,'k','LineWidth',2)

xlabel('Gate Voltage,V G S (V)')

ylabel('\phi_s_f (V),\phi_s_b (V),\phi_s_b_u_l_k (V)')

legend('Model','Iteration',2)%2 means top left corner, 4 means top right corner

text(0.57,0.68, '\phi_s_b_u_l_k')

text(0.57,0.9, '\phi_s_b')

text(0.57,0.98, '\phi s f')

% %Relative error calculation section between analytical and numerical model

% %To calculate relative error Vgs and Vgsi must be same size

% % % x=((phi sf-phi sf iter)./phi sf iter)*100;

% y=((phi_sb_phi_sb_iter)./phi_sb_iter)*100;

% z=((phi sbulk-phi sbulk iter)./phi sbulk iter)*100;

\% figure(\overline{4})

% plot(Vgs, abs(x))

% hold on

% plot(Vgs,abs(y))

% hold on

% plot(Vgs,abs(z))

% Effect of substrate charge on the Surface Potential phi sbulk calc for

% different Nsub, where Vcb=0

```

```