Assimilation of negative feedback in Bandgap reference circuits for subsiding the variation of reference voltages over the temperature range from -55°C to +165°C

By

Syed Ziaul Haque Md.Rashed Uzzaman Abdullah-Al-Mamun

Submitted to

# The Department of Electrical and Electronic Engineering

**Faculty of Science and Engineering**

East West University

In partial fulfillment of the requirements for

The degree

Of

Bachelor of Science in Electrical & Electronics Engineering

(B.Sc. in EEE)

Fall, 2011

# APPROVAL

The project titled "Assimilation of negative feedback in Bandgap reference circuits for subsiding the variation of reference voltages over the temperature range from  $-55^{\circ}$ C to  $+165^{\circ}$ C." submitted by Syed Ziaul Haque (2008-1-80-061), Md.Rashed Uzzaman (2008-1-80-035) and Abdullah-Al-Mamun (2008-1-80-067), has been accepted as satisfactory in partial fulfillment of the requirements for the degree of Bachelor in Science in Electrical and Electronic Engineering on Fall 2011.

Rative

S. M. Shahriar Rashid (Supervisor)

Lecturer

Department of Electrical and Electronic Engineering,

East West University, Dhaka.

pre- 22.01.2012

Dr. Anisul Haque Professor & Chairperson Department of Electrical and Electronic Engineering

East West University, Dhaka.

# AUTHORIZATION

We hereby declare that we are the sole authors of this thesis and it has not been submitted elsewhere for the award of any degree or diploma. We authorize East West University to lend this thesis to other institutions or individual on request for the purpose of scholarly research only. We further authorize East West University to reproduce this thesis by photocopy or other means in total or in part at the request of other institutions or individuals for the purpose of scholarly research only.

Countersigned

Balive

S. M. Shahriar Rashid (Supervisor)

Lecturer

Department of Electrical and Electronic Engineering,

East West University, Dhaka.

Signature of the students

Syed Ziaul Haque

Rashed

Md.Rashed Uzzaman

Abdullah - Al - Mamma

Abdullah-Al-Mamun

# TABLE OF CONTENTS

|     | TAE        | LE OF CONTENTS                                              | ŀ |

|-----|------------|-------------------------------------------------------------|---|

|     | LIS        | ۲ OF FIGURES                                                | ĵ |

|     | LIST       | Γ OF TABLES                                                 | 7 |

|     | ACH        | KNOWLEDGEMENTS                                              | ŝ |

|     | ABS        | TRACT                                                       | ) |

|     | CHA        | APTER I                                                     | ) |

| 1.1 | 1<br>Mot   | Introduction                                                |   |

| 1.2 | Liter      | ature review                                                | ) |

| 1.3 | Thes       | is Objective                                                | 1 |

| 1.4 | Over       | rview                                                       | 2 |

|     | CH         | APTER II                                                    | 3 |

| 2.1 | 2<br>Intro | Bandgap Reference Circuit                                   |   |

| 2.2 | Supp       | ply-independent Biasing                                     | 3 |

| 2.3 | Tem        | perature-independent references                             | 5 |

| 2.3 | .1         | Negative- TC voltage                                        | 5 |

| 2.3 | .2         | Positive-TC Voltage                                         | 7 |

| 2.3 | .3         | Bandgap Reference                                           | 3 |

| 2.3 | .4         | Collector current Variation                                 | 1 |

| 2.4 | Com        | patibility with CMOS Technology                             | 2 |

| 2.5 | PTA        | Current Generation                                          | 2 |

| 2.6 | Ban        | dgap Circuit and Simulation Result                          | 4 |

| 2.6 | 5.1        | General discussion                                          | 4 |

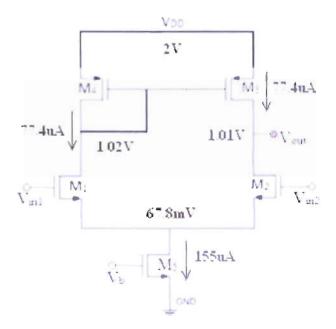

| 2.6 | 5.2        | Circuit description                                         | 4 |

| 2.7 | Sim        | ulation result                                              | 5 |

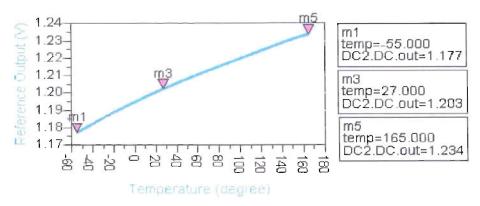

| 2.7 | 7.1        | The effect of temperature variation in the reference output | 5 |

|     | 2.7.1.:    | 1 The effect of process variation in the reference output   | 7 |

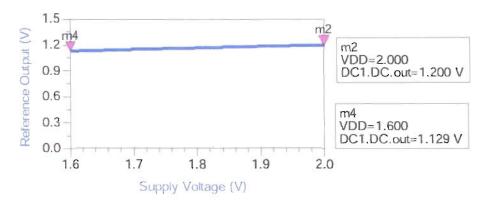

|     | 2.7.1.     | 2 The effect of supply variation in the reference output    | 8 |

| 2.8 | Sum        | mary                                                        | 9 |

|      | CHA        | APTER III                                      | 30              |

|------|------------|------------------------------------------------|-----------------|

|      | 3          | Operational Amplifier                          |                 |

| 3.1  |            | duction                                        |                 |

| 3.2  |            | stage differential-amplifier                   |                 |

| 3.3  |            | gning procedure                                |                 |

| 3.4  |            | lation results                                 |                 |

| 3.4. | .1         | Effect of Temperature variation                | 33              |

| 3.4. | .2         | Effect of Supply variation                     | 35              |

| 3.5  | Sumi       | mary                                           | 37              |

|      | CHA        | APTER IV                                       |                 |

| 4.1  | 4<br>Intro | Proposed Bandgap Reference Circuit             | <b>38</b><br>38 |

| 4.2  | Nega       | tive feedback mechanism                        | 38              |

| 4.3  | First      | proposal                                       | 38              |

| 4.3  | .1         | Circuit description                            | 38              |

| 4.3  | .2         | Summary                                        | 39              |

| 4.4  | Seco       | nd proposal                                    | 40              |

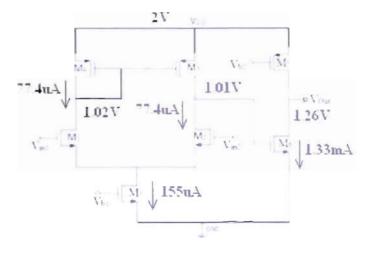

| 4.4  | .1         | Circuit Description                            | 40              |

| 4.4  | .2         | Summary                                        | 41              |

| 4.5  | Conc       | lusion                                         | 41              |

|      | CHA        | APTER V                                        | 42              |

| 5.1  | 5<br>Futu  | Conclusion                                     |                 |

| 5.2  | Proje      | ect summary                                    | 42              |

| A.1  |            | endix A<br>vanced Design System (ADS) Tutorial |                 |

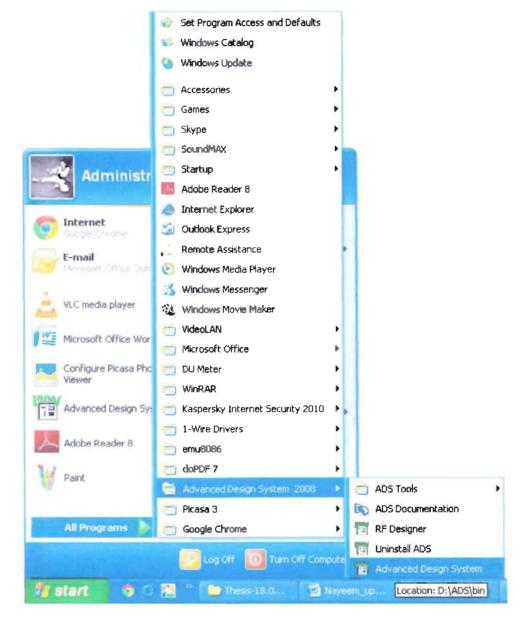

| A.1  | .1 In:     | stallation of ADS                              | 43              |

| Ļ    | A.1.1.1    | 1 Before installation procedure                | 43              |

| Þ    | A.1.1.2    | 2 Installation of license key                  | 43              |

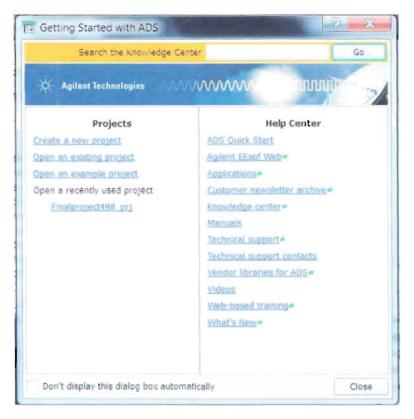

| A.1  | .2 Si      | imulation process in ADS                       | 44              |

| 1    | A.1.2.1    | 1 Creating a Project in ADS                    | 45              |

| ,    | 4.1.2.2    | 2 Installation of the design kit               | 46              |

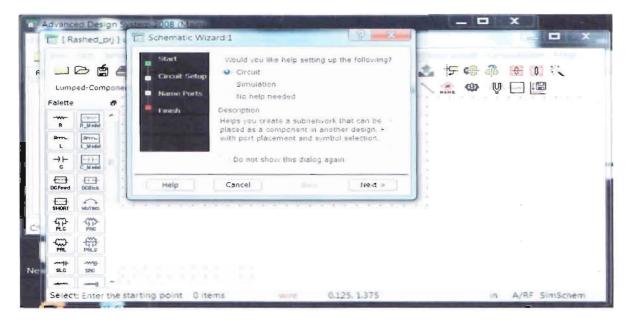

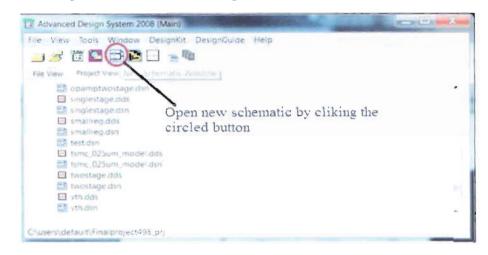

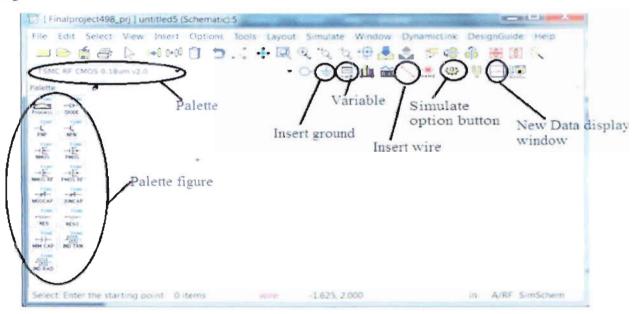

| 1    | A.1.2.3    | 3 Design in ADS                                | 48              |

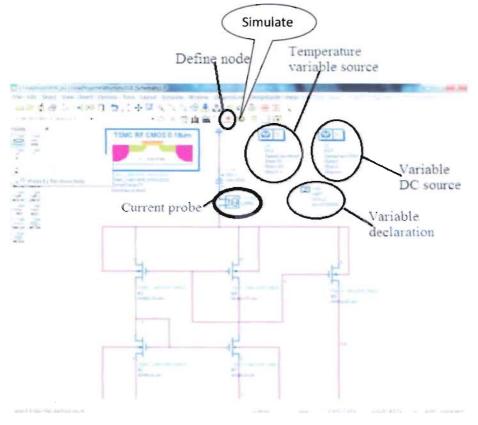

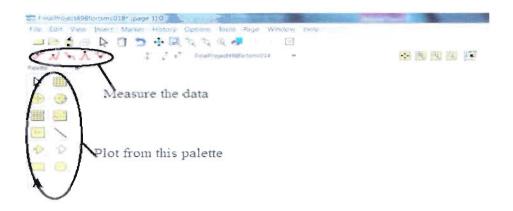

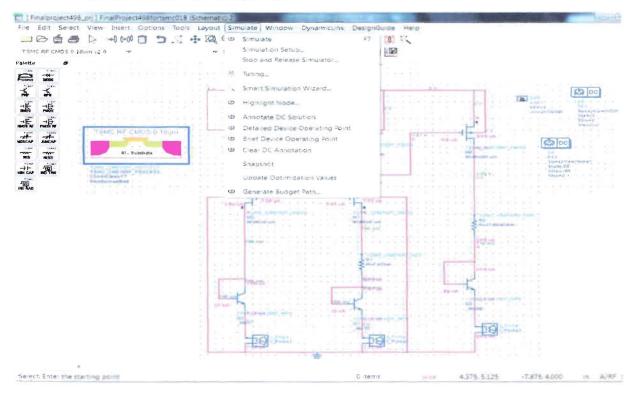

| ŀ    | 4.1.2.4    | 4 Simulation in ADS                            | 50              |

|      | Refe       | crcnccs                                        | .53             |

# LIST OF FIGURES

## Page

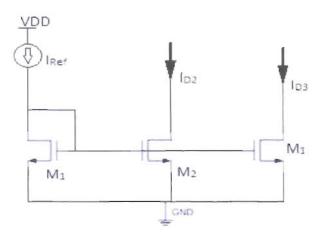

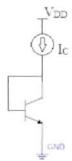

| Figure 2-1: Current biasing using an ideal current source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

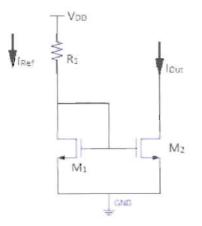

| Figure 2-2: Current mirror biasing using a resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 2-3: Simple circuit to establish supply-independent currents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 2-4: Set up for negative TC15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

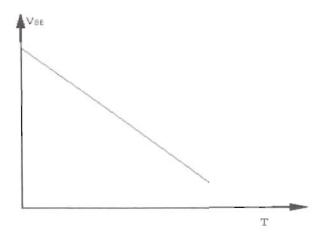

| Figure 2-5: Negative sloping line for the TC of V <sub>BE</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

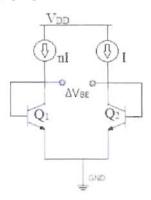

| Figure 2-6: Generation of PTAT voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

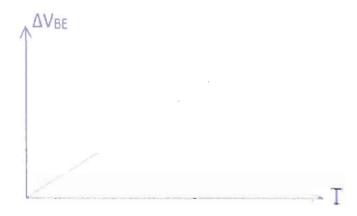

| Figure 2-7: Positive sloping line for the TC of $\Delta V_{BE}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 2-8: Conceptual generation of temperature-independent voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 2-9: Actual implementation of the Conceptual generation of temperature-independent voltage 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

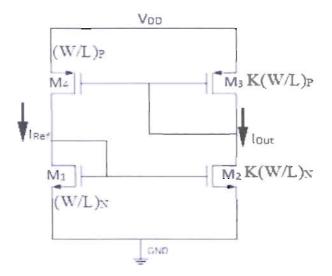

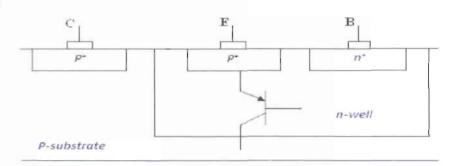

| Figure 2-10: Realization of p-n-p bipolar transistor in CMOS technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

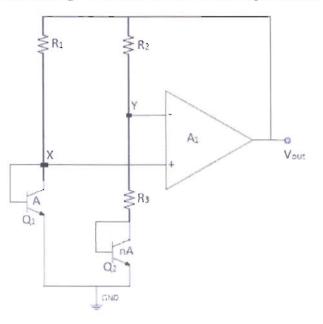

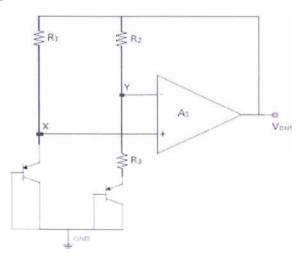

| Figure 2-11: Conceptual generation of temperature-independent voltage with p-n-p transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

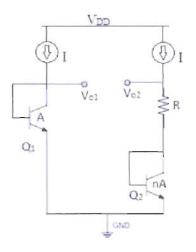

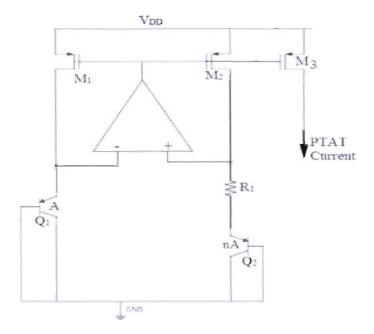

| Figure 2-12: Generation of a PTAT current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

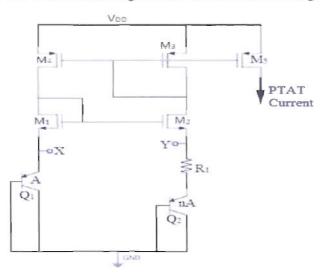

| Figure 2-13: Generation of a PTAT current uses a simple amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

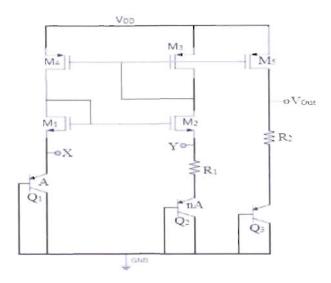

| Figure 2-14: Generation of a temperature- independent voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

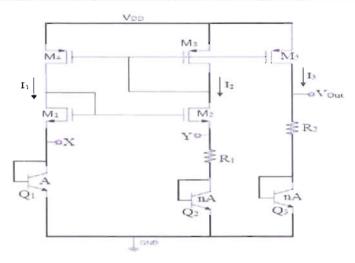

| Figure 2-15: Bandgap Reference circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

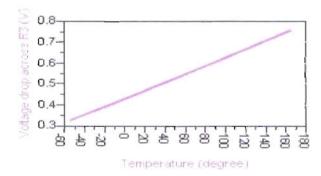

| Figure 2-16: Voltage variation across R <sub>2</sub> with temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

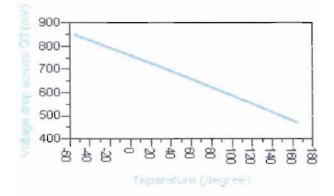

| Figure 2-17: Voltage variation across Q <sub>3</sub> with temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

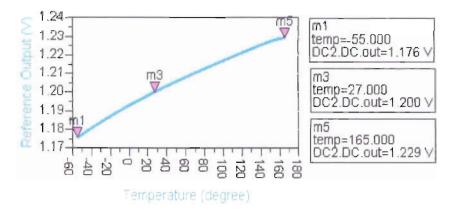

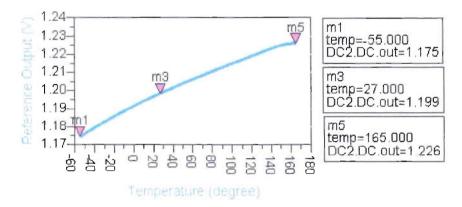

| Figure 2-18: Variation of reference voltage with temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 2-19: Variation of reference voltage with temperature when resistances are increased by 25%27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 2-20: Variation of reference voltage with temperature when resistances are decreased by 25%. 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 2-21: Reference output with varying supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure 3-1: Input stage Op Amp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figure 3-2: Two stage Op Amp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

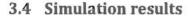

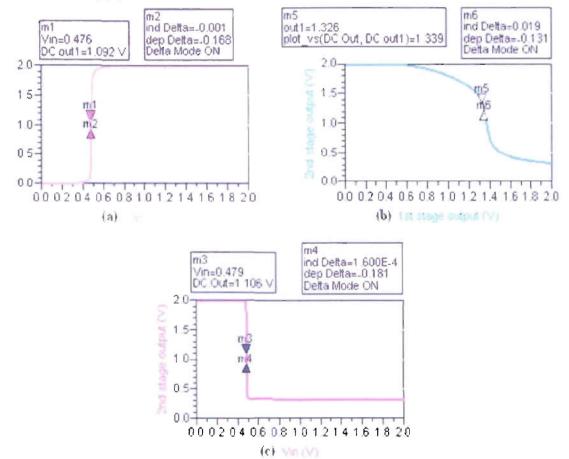

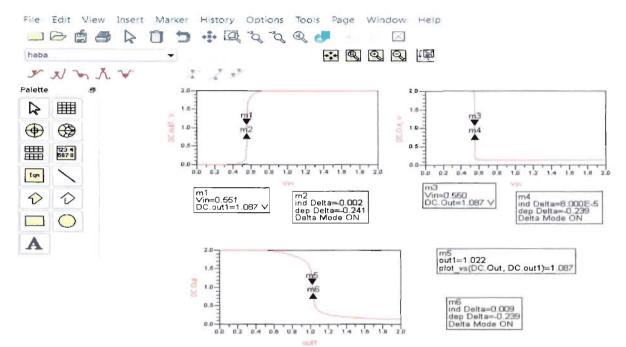

| Figure 3-3: Variation of output voltages with respect to the inputs of different stages of the Op Amp for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| biasing voltage of 1.2V at 27°C (a) 1st stage (b) 2 <sup>nd</sup> stage (c) overall voltage variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

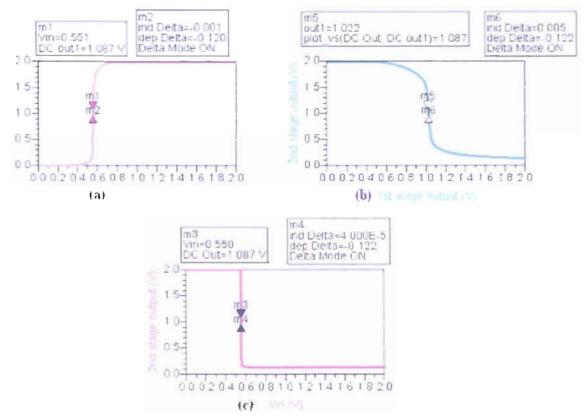

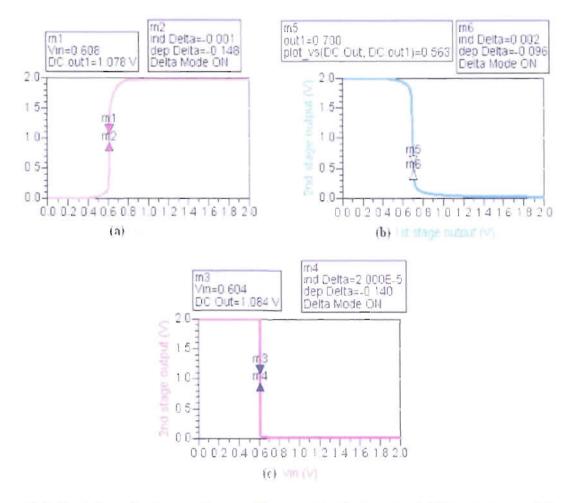

| Figure 3-4: Variation of output voltages with respect to the inputs of different stages of the Op Amp for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| biasing voltage of $1.229V$ at $+165^{\circ}C$ (a) 1 <sup>st</sup> stage (b) 2 <sup>nd</sup> stage (c) overall voltage variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

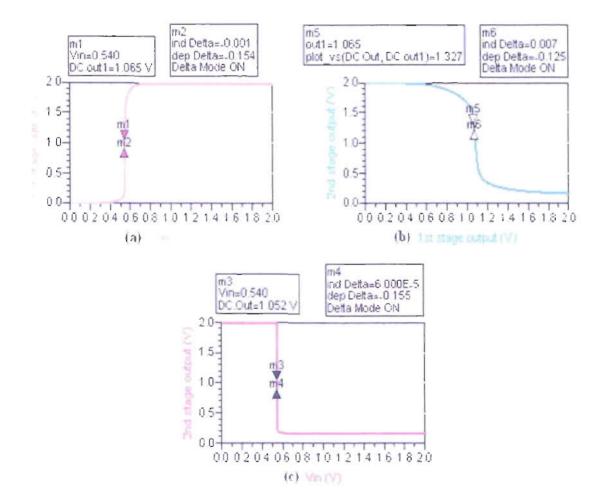

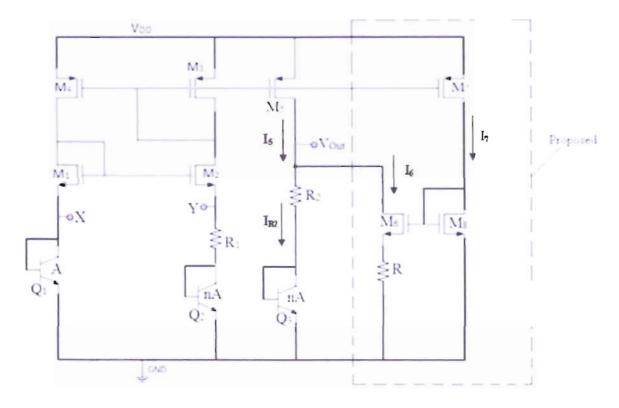

| Figure 3-5: Variation of output voltages with respect to the inputs of different stages of the Op Amp for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| biasing voltage of 1.176V at -55°C (a) 1 <sup>st</sup> stage (b) 2 <sup>nd</sup> stage (c) overall voltage variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

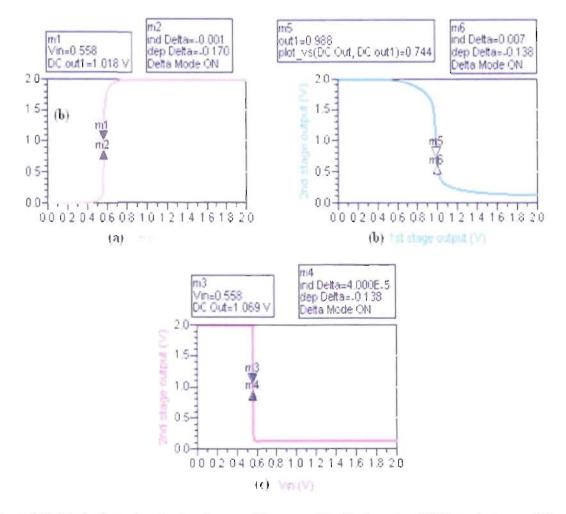

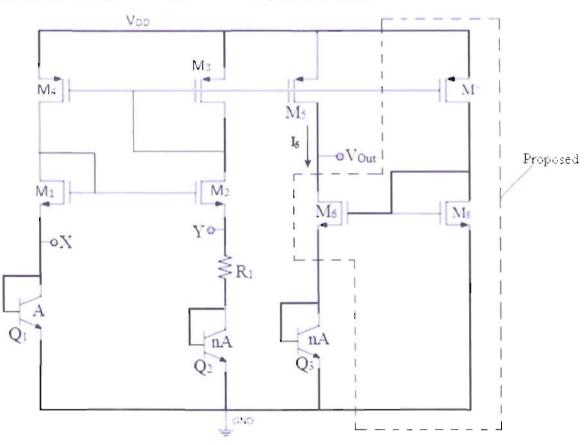

| Figure 3-6: Variation of output voltages with respect to the inputs of different stages of the Op Amp when the supply voltage is increased from $2V to 3V$ (a) $1^{st}$ stage (b) $2^{nd}$ stage (c) overall voltage variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 3-7: Variation of output voltages with respect to the inputs of different stages of the Op Amp when the supply voltage is decreased from 2V to 1V (a) 1 <sup>st</sup> stage (b) 2 <sup>rd</sup> stage (c) overall voltage variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |