#### **DEGRADATION OF EFFECTIVE DECOUPLING CAPACITANCE IN HIGH SPEED CMOS CIRCUITS**

By

ZUBAER IBNA MANNAN MD. ATIKUL ISLAM MD. SHAMIUN HOSSAIN

Submitted to the

Department of Electrical and Electronic Engineering Faculty of Sciences and Engineering East West University

In partial fulfillment of the requirements for the degree of Bachelor of Science in Electrical and Electronic Engineering (B.Sc. in EEE)

Spring, 2010

Approved By

Chairperson

Thesis Advisor

DR. MD. ISHFQUR RAZA

DR. ANISUL HAQUE

3 AUG 2010

#### Abstract

te to increasing demand on power by silicon operating at higher frequencies, voltage droops in wer buses at switching transients can be a critical constraint. On-die decoupling is used to luce the droops and achieve higher performance. In this thesis we perform an analysis of high equency decoupling capacitor design using low loss tangent high-k material as dielectric. These pacitors can be used effectively at higher frequencies and can able to compensate the voltage pop to ensure the constant power delivery. We also consider the performance degradation of e decoupling capacitor at high frequency. It is noted that dielectric material effective pacitance reduces above several GHz due to the degradation of the dielectric constant. Below ese frequencies it is demonstrated that decoupling capacitors have better performance at highequency if the high-k material has lower loss tangent. For this reason we choose lower loss ogent high-k material to design the decoupling capacitor and placed them closer to CMOS recuits. Our analysis is done on the basis of simulation result done using the ADS software hich is briefly discussed inside this paper.

#### Acknowledgements

We are so much thankful to our supervisor Dr. Md. Ishfaqur Raza because without his special care and helpful hand we couldn't complete the project successfully. He tried so hard and gives us much more time to know the depth of knowledge which is related with our project. He motivated and guided us successfully to understand that what we are going to do and what are the factor we need to know to complete it. So again we want to give him thanks from our heart and pray to "ALLAH" to keep him safe & happy.

We want to give our special thanks to our Chairpersons of EEE department, Dr. Anisul Haque to give us the opportunity and allow us for undergraduate thesis program. We are also so grateful to other faculty members of EEE department that they are supporting us to complete our job. Especially Dr. Khairul Alam, Khondker Zakir Ahmed, Mohammad Salauddin, S. M. Shahriar Rashid are tried thelp us from their sides.

We can't forget of our senior brothers and sisters' help and contribution to complete this project, specially Ophelia Mohaimen and her group members who are already completed their project & sesis paper which is close to our project & thesis paper. So we so much information and help from sem to done our job.

e VLSI lab officer Jubayer Ahmed is trying to give us his full support to use the lab which is portant part of our project. So we thank him to help us in our work. We also want to thank the sole office stuff of the EEE department for their special care to us.

Authorization page

I hereby declare that I am the sole author of this thesis. I authorize East West University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

Anik

Zubaer Ibna Mannan

Md. Atikul Islam

Md. Shamiun Hossain

further authorize East West University to reproduce this thesis by photocopy or other means, total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Attive

2ubaer Ibna Mannan

Md. Atikul Islam

Md. Shamiun Hossain

# TABLE OF CONTENTS

| 1. IN                    | TRODUCTION                                                                                                                                                                                                                                                                              |                                                    |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1.1<br>1.,<br>1.,<br>1., | MOTIVATION:<br>LITERARY SURVEY:<br>2.1 Decoupling Capacitor:<br>2.2 White Space or White Area Decoupling:<br>2.3. Voltage Droops:<br>2.4. Dielectric Constant & Loss Tangent:<br>2.5. High K Materials:<br>PROPOSAL OF DECOUPLING CAPACITOR:                                            | 9<br>                                              |

| 1. PC                    | OWER DELIVERY IN HIGH FREQUENCY CIRCUIT                                                                                                                                                                                                                                                 | 13                                                 |

| 3. NO                    | OVEL METHOD OF REDUCING POWER DROOP                                                                                                                                                                                                                                                     |                                                    |

| 3.1.<br>3.2.<br>3.3.     | IMPROVED VLSI CIRCUIT PERFORMANCE USING LOCALIZED POWER DECOUPLING:<br>LOW-COST DEEP TRENCH DECOUPLING FOR LOW-POWER CMOS:<br>A DECOUPLING PLATFORM FOR SUBSTRATES, SOCKETS, AND INTERPOSERS:                                                                                           |                                                    |

| 4. HI                    | IGH-K DIELECTRIC CONSTAN WHY NEED HIGH-K?                                                                                                                                                                                                                                               |                                                    |

| =.1.<br>: <u>2.</u>      | HIGH-K DIELECTRICS:                                                                                                                                                                                                                                                                     |                                                    |

| 5. SI                    | MULATION & ANALYSIS                                                                                                                                                                                                                                                                     | 24                                                 |

| 5.9,                     | MAIN CIRCUIT:<br>ESL & ESR:<br>WHY & WHERE TO PLACE DECOUPLING CAPACITOR:<br>INDUCTIVE DROP - L <sup>D:</sup> LOSS:<br>REDUCE PATH INDUCTANCE L:<br>WHITE AREA:<br>DESCRIPTION ON ADS:<br>RESULT & CALCULATION:<br>S.1. Calculation To Make The Capacitance Same:<br>SIMULATION RESULT: | 25<br>26<br>27<br>28<br>29<br>29<br>29<br>31<br>32 |

| Pſ                       | ROPOSED CAPACITOR COMPONENTS                                                                                                                                                                                                                                                            |                                                    |

| ::<br>- <u>-</u>         | WHY WE USE HIGH-K MATERIAL IN DESIGNING CAPACITOR:                                                                                                                                                                                                                                      |                                                    |

| - C(                     | ONCLUSION                                                                                                                                                                                                                                                                               |                                                    |

| RI                       | JTURE WORK                                                                                                                                                                                                                                                                              |                                                    |

| 2.0                      | SDIX                                                                                                                                                                                                                                                                                    | 49                                                 |

# LIST OF ILLUSTRATIONS

| Figure 1: Transistor count doubles every 18-24 months                                                                                               |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2 : Increase in supply current for Microprocessor in future                                                                                  |    |

| Figure 3: Power delivery solution for the Pentium 4 processor                                                                                       |    |

| Figure 4: Equivalent model of power delivery system in microprocessor                                                                               |    |

| Figure 5: simple model of Power Delivery Analysis circuit                                                                                           |    |

| Figure 6 : The Equivalent Series Resistance, ESR associated with a capacitor25                                                                      |    |

| Figure 7 : Capacitor equivalent circuit                                                                                                             |    |

| Figure 8: Plot frequency vs. impedance                                                                                                              |    |

| Figure 9 : Power Delivery Analysis circuit                                                                                                          |    |

| Figure 10 : Placement of decoupling capacitance                                                                                                     |    |

| Figure 11 : Placement of on-chip decoupling capacitors using a conventional approach in                                                             |    |

| white area                                                                                                                                          |    |

| Figure 12: Momentum window of ADS                                                                                                                   |    |

| Figure 13 : Schematic window of ADS                                                                                                                 |    |

| Figure 14 : Without decoupling capacitance voltage droop                                                                                            |    |

| Figure 15: Showing voltage droop for HfO <sub>2</sub> and La <sub>2</sub> O <sub>3</sub> at 0.1ns edge rate                                         |    |

| Figure 16: Simulation result which shows voltage droop for $SiO_2$ , $HfO_2$ and $La_2O_3$ at 0.1n                                                  | IS |

| edge rate                                                                                                                                           |    |

| Figure 17: Showing voltage droop for HfO <sub>2</sub> and La <sub>2</sub> O <sub>3</sub> at 0.01ns edge rate                                        |    |

| Figure 18: Simulation result which shows voltage droop for SiO <sub>2</sub> , HfO <sub>2</sub> and La <sub>2</sub> O <sub>3</sub> at 0.01 edge rate | ns |

| Figure 19: Showing voltage droop for HfO <sub>2</sub> and Y <sub>2</sub> O <sub>3</sub>                                                             |    |

| Figure 20: Showing the power factor angle where Js is leads E to determine loss tangent.3                                                           | 38 |

| Figure 21: Equivalent model of a capacitor and its loss tangents relation                                                                           |    |

| Figure 22: Initially without applied voltage V & after applied voltage V                                                                            |    |

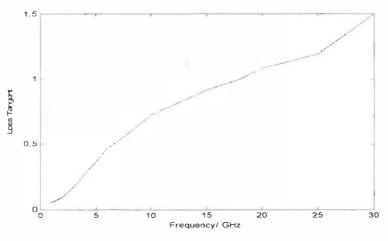

| Figure 23: Change in loss tangent of water with frequency                                                                                           |    |

| Figure 24: Simulation result without using decoupling capacitor                                                                                     |    |

| Figure 25: Simulation result when placing decoupling capacitor by using HfO <sub>2</sub> and La <sub>2</sub> O <sub>3</sub> material                |    |

| Figure 26: The ADS substrate layers window showing the declaration parameter while designing capacitor                                              |    |

| Figure 27: The ADS Layout layers window showing the declaration parameter while                                                                     |    |

| designing capacitor                                                                                                                                 |    |

# LIST OF TABLES

|                                                                                 | <u>Page</u> |

|---------------------------------------------------------------------------------|-------------|

| Table 1: Change of voltage level for future technology predict by ITRS          | J4          |

| Table 2: Key parameters of high-k dielectrics evaluated                         | 23          |

| Table 3: The value we used for the equivalent parameter in main circuit         | 25          |

| fable 4: The value we used for the equivalent capacitor parameter               | 25          |

| Table 5: High-k materials with dielectric constant and loss tangent             |             |

| Table 6: The data for equivalent oxide thickness for future technology given by | ITRS 36     |

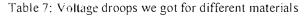

| Table 7: Voltage droops we got for different materials                          |             |

# 1. INTRODUCTION

# HST University HST HST HST HST HST HST HST HOhakhall

#### 1.1. Motivation:

In semiconductor circuit one of the most unfortunate features is parasitic component which causes voltage droop. To solve this voltage droop problem we can use a decoupling capacitor, familiarly known as "decaps", in shunt with the driving load and which can provide the required voltage to the driving load. But decoupling capacitors properly work only within a certain frequency bandwidth. If the frequency content of the signal increases the effective capacitance of the decoupling capacitor decreases, particularly at very high frequency. This will eventually reduce the effectiveness of the decoupling capacitor behaves like a short circuit for which at high frequency the circuit voltage droop can not then be compensated. But if we change the dielectric material then we have an opportunity to increase the frequency response of the capacitor. So our proposal is to look at different materials including High-K.

Basically high-k material can increase the sustainability of capacitor in high frequency due to its higher dielectric constant and lower loss tangent. Loss tangent is a dielectric material parameter which quantifies its inherent dissipation of electromagnetic energy. Actually it refers to an angle in a complex plane between the resistive (lossy) component of an electromagnetic field and its reactive flossless) component. If the loss tangent of a dielectric material decreases then its frequency increases by the below relationship,

#### $f = \sigma/2\pi\epsilon' tan\delta$

The dielectric constant [1] refers how effective a dielectric is allowing a capacitor to store more charge depends on the dielectric material from which it made off. Every material has a dielectric constant k and it is the ratio of the field without the dielectric  $(E_0)$  to the net field (E) with the dielectric,  $k = E_0 / E$ . Benefit of the larger the dielectric constant is that it can store more charges. So, if we build capacitor with large dielectric constant and less loss tangent then we can build such a material which is smaller in size but can operate in a comparatively high frequency and the performance of the capacitor is far better than any other normal material made capacitor.

We have discussed above that for better performance of the capacitor we need high-K material but it as a big impact on the size of the capacitor. Basically, Silicon dioxide has been used as a gate oxide

material for decades. As transistors have decreased in size, the thickness of the silicon dioxide gate dielectric has gradually decreased to increase the gate capacitance and thereby drive current and device performance. As the thickness scales below 2 nm, leakage currents occur due to electron tunneling increase significantly, leading to unwieldy power consumption and reduced device reliability. Replacing the silicon dioxide gate dielectric with a high -K material allows increased gate capacitance without the concomitant leakage effects and with an acceptable small size.

For the above consideration our motivation is to build a capacitor with high-K material such as hafnium dioxide (HFO<sub>2</sub>), Yttrium Oxide(Y<sub>2</sub>O<sub>3</sub>) and Lanthanum Oxide (La<sub>2</sub>O<sub>3</sub>) which can store a large amount of charge and can sustain in a comparatively high frequency with small size and also observe the capacitance of these three materials with respect to frequency.

#### 1.2. Literary Survey:

#### 1.2.1. Decoupling Capacitor:

Decoupling capacitor is one kind of capacitor which is used to provide charge support to switching circuits. Electrical circuit noise caused by a circuit element can affect other circuit elements by modifying the voltage rail levels. To deduce this problem a capacitor is shunted after that noise creating element which eventually reduce the effect they have on the rest of the circuit. Bypass capacitor is the alternative name of a decoupling capacitor; as it is used to bypass the power supply r other high impedance component of a circuit.

In "High Capacitance, Large Area, Thin Film. Nanocomposite Based Embedded Capacitor[1]" taper, they represented thin film technology based on barium titanate (BaTiO<sub>3</sub>)-epoxy polymer composites to develop and manufacture high performance embedded capacitors and can be used in decoupling purpose. The referred technology was able to produce high capacitance density (10 to 90 nF/inch2), large area, and thin film capacitors with controlled thickness from about 2 micron to pout 25 microns for a series of BaTiO3 epoxy nanocomposites.

"Layout of Decoupling Capacitors in IP Blocks for 90-nm CMOS [2]" paper, they introduced a sign metric to determine the optimal number of fingers to use in the standard cell layout to obtain a desired capacitance level over a target operating frequency and investigated the tradeoffs between

high-frequency performance of decaps and electrostatic discharge (ESD) protection and its impact on the layout of standard cell decaps.

In "Efficient Placement of Distributed On-Chip Decoupling Capacitors in Nanoscale JCs [3]" paper they proposed a system of distributed on-chip decoupling capacitors where on-chip decoupling capacitor is providing the required on-chip decoupling capacitance under existing technology constraints. In this system of distribution a capacitor is placed closest to the current load to provide the required charge and as the first capacitor is depleted, the next decoupling capacitor is activated to provide a large portion of the total current drawn by the load.

#### 1.2.2. White Space or White Area Decoupling:

White space refers to the unused blank space in a semiconductor device. Now a day's semiconductor chips are very small in size so we need to manage our redundant space effectively. As we use a lecoupling capacitor in the semiconductor device to compensate the voltage droop so, that accoupling capacitor can be placed in that white space or white area region.

" "Quantifying Decoupling Capacitor Location [4]" paper, they discuss about the position of the accoupling capacitor. Coupling between an IC and a decoupling capacitor is a function of the macing between the IC and capacitor, and spacing between power and ground layers. They studied the impact of the mutual inductance on decoupling, i.e., local versus global decoupling by using a mutual extraction approach based on a mixed-potential integral equation where local decoupling thite area decoupling near the required load) has benefits over global decoupling for certain ranges IC/capacitor spacing and power layer thickness.

#### 1.2.3. Voltage Droops:

Itage droop defines the unintentional drop in voltage level due to current drawn by switching uits. It occurs due to the path inductance and resistance. Although small amounts of voltage op are unavoidable, there are times when voltage droop is excessive and can cause unexpected i unwanted behavior in a circuit. To prevent voltage droop, decoupling capacitors should be used compensator to compensate the current needed to drive the load.

"Test Pattern Generation for Power Supply Droop Faults [5]" paper, they represented about a new using of droop faults (basically timing fault) to explain the timing behavior in a faulty circuit

induced by power supply voltage drop in nano-scale VLSI chips. In new modeling a simple ATPG (Automatic Test Pattern Generation) based procedure for stuck-at faults has been adapted to test Broop faults where for validation of the methodology in combinational circuits, a set of appropriate clusters of gates is selected to cover potential droop-prone regions in a circuit.

In "Decoupling Capacitors for Multi-Voltage Power Distribution Systems [6]" paper they investigated the dependence of the impedance and magnitude of the voltage transfer function on the parameters of the power distribution system and explained an anti-resonance phenomenon. They showed that the magnitude of the voltage transfer function is strongly dependent on the parasitic inductance of the decoupling capacitors. So they design a technique to cancel and shift anti-resonant spikes out of range of the operating frequencies for which the decoupling capacitor can perform its required operation properly.

#### 1.2.4. Dielectric Constant & Loss Tangent:

ne loss tangent is a parameter of a dielectric material that refers the inherent dissipation of detromagnetic energy. Basically this term defines an angle in a complex plane between the desistive (lossy) component and reactive (lossless) component of an electromagnetic field.

The dielectric constant is the ratio of the permittivity of a substance (material) to the permittivity of the space. So, dielectric constant,  $\varepsilon = \varepsilon_0/\varepsilon_r$  where  $\varepsilon_0$  represents the field without the dielectric and  $\varepsilon_r$  appresents the field with the dielectric.

#### 1.2.5. High K Materials:

$\pm$  k materials are material which has a higher dielectric constant ( $\epsilon_r$  or K). High-k materials are  $\pm$  in semiconductor manufacturing processes which replace the silicon dioxide gate dielectric.

The implementation of high-k gate dielectrics has developed several strategies to allow further miniaturization of microelectronic components, colloquially referred to as extending Moore's Law.

In "Recent Advances in High-k Nanocomposite Materials for Embedded Capacitor Applications [8]" paper, they discuss about the high dielectric constant (k) composite materials which have been developed and evaluated for embedded and decoupling capacitor application where they try to achieve high dielectric performance including high-k and low dielectric loss for polymer composites. In this paper the referred high-k materials which meet the requirements for this application should possess high dielectric constant, low dissipation factor, high thermal stability, simple process ability and good dielectric properties over broad frequency range.

#### 1.3. Proposal of Decoupling Capacitor:

in this paper we propose a decoupling capacitor model to compensate the voltage droop of the affected power delivery system of the semiconductor device and investigate the performance degradation of the decoupling capacitor at high frequency for the different high-k materials.

For capacitor we use high-k materials due to scale down effects of SiO<sub>2</sub> gate oxide, while maintaining lower power consumption and increased performance of the decoupling capacitor at high frequencies. If we scale down the gate oxide then electron tunneling occurred in VLSI circuits but if we use the high-k materials which has the higher dielectric constant then can reduce electron tunneling by virtue of using a thicker dielectric. Although a material has higher dielectric constant but if the material has higher loss tangent then the capacitor made of that material becomes a lossy capacitor, thus performance degradation of high frequency. But fortunately almost all the high-k material has lower loss tangent compare to Silicon for which they can sustain acceptable performance at high frequency. For the above stated reason we chose three different high-k materials to design the stack capacitor to show the performance degradation at high frequency.

# 2. POWER DELIVERY IN HIGH FREQUENCY <u>CIRCUIT</u>

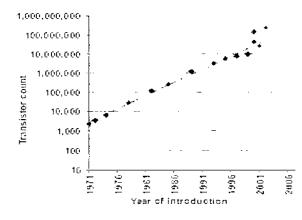

According to Moore's Law, the number of transistor is increasing exponentially. The increasing number of transistors over the past several decades in microprocessor is shown in Fig. 1.

Figure 1: Transistor count doubles every 18-24 months.

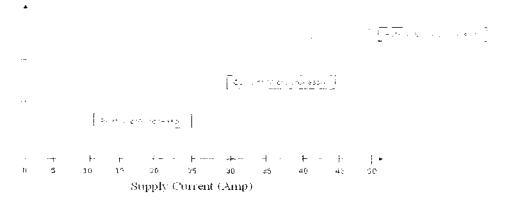

It is also known that these transistors need to switch faster to improve its performance because the more the transistors switch fast then we can get better performance from the microprocessor chip. As ransistor are getting smaller and faster, over the last two decades the current levels of the microprocessor has also been increasing dramatically. This high current was delivered from the two supply on the system motherboard to the chip through the package. To handle this high current, the package must provide a low resistance path in the order of <1mOhm. In Fig. 2 we sticed that at present the typical supply current is in 10-30 A range, also a range that is expected to orcease for future microprocessor [9].

Figure 2 : Increase in supply current for Microprocessor in future.

increase in current consumption by the microprocessor is also demanding that the reduction of voltage level of the microprocessor. International Technology Roadmap for Semiconductor RS) published 'Roadmap Information' about future technology requirements for semiconductor rry year. If we look over ITRS 2009 Edition then we see the projected reduction in voltage level or the next couple of years, Table 1.

Table 1: Change of voltage level for future technology predict by ITRS

| Ycar       | 2009              | 2010 | 2011     | 2012 | 2013 | 2014 | 2015 |

|------------|-------------------|------|----------|------|------|------|------|

| – Volts (' | V) <sup>°</sup> 1 | 0.97 | <u> </u> | 0.9  | 0.87 | 0.84 | 0.81 |

the reduction of power supply voltage is also decreasing noise margin. The paper published by Y.-Jiang, K.-T. Cheng, "Analysis of Performance Impact Caused by Power Supply Noise in Deep (bmicron Devices," in 1999 shows that around 10-15% voltage drop may cause 20-30% increase in the propagation delay. So for most of the 90 nm static CMOS gates a change of 1% in power upply voltage may occur to nearly 4% change in delay. The delay of a logic gate increases when here is a supply voltage drop across the gate.[10]

this situation we can say that as CM $\odot$ S technology scales day by day so the power supply has become a big issue because of increasing clock frequency and decreasing supply voltage. As a result then several transistors switch simultaneously then a significant power supply drop will be happen. It is power supply drop is happening because there are parallel load across the power grid. This tenomenon is known as voltage droop.

modern high speed system resistive IR and inductive L(di/dt) voltage drops are the main urce of voltage droops. The IR droop has been increasing due to increased resistance in the power d because of reduced widths of the metal as technology becomes more advanced. Also in CM $\odot$ S choology the demand of high current is increasing that's why the effect of L (di/dt) is increased  $\gamma$  by day. [11] So when devices are switching with respect to the clock edge, then it will draw trent to charge or discharge CMOS gate capacitances. As a result at the edge of clock the voltage ps at the parasitic elements is observed which is reduces the power rail voltage, or  $V_{ee}/V_{dd}$ . This unction in supply voltage due to switching is known as power supply noise. The increase in vor supply noise reduces the signal noise margin, increases signal delay, delay uncertainty and N jitter.

÷

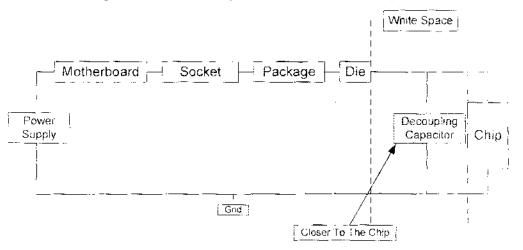

So we need to implement and consider power distribution in a digital system which is given below.

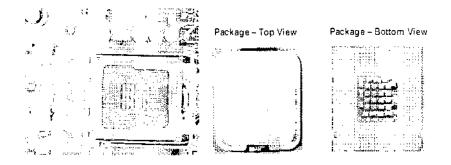

• One of the most effective ways to reduce the power supply noise is to use decoupling capacitor on the card, board, module and chip. Here decoupling capacitors worked as a charge storage device so that it can oppose the voltage droops at the edge of clocks at different stages of the network. However, these capacitors are controlled by their location with respect to the CMOS devices and their inherent parasitic components (such as equivalent series resistance and inductance, i.e. ESR and ESL). The placing of the decoupling capacitor in a power delivery system is shown in Fig. 3 & 4.

Figure 3: Power delivery solution for the Pentium 4 processor.

Figure 4: Equivalent model of power delivery system in microprocessor.

The power is delivered to the chip after passing through the motherboard, socket and package. Using this power delivery, there will be loss (L, R loss). Decoupling capacitor are used as local using reservoir. So decoupling capacitor is placed closer to the chip so that it can provide extra

current to charge the load capacitor in addition to the power supply. Also it will reduce power supply noise because the inductive effect in the loop current path is decreased. As the inductance scales slowly, the placement of decoupling capacitor is very important because it affect the performance of power supply network as well as the chip performance.

The performance of decoupling capacitor depends on the distance between the current load and the decoupling capacitance. Decoupling capacitor should be placed close to a current load during discharge and once the switching event is completed then decoupling capacitance should be charged before the next clock cycle starts.[12]

Decoupling capacitors are generally placed in white space available on the die. To get effective performance physically decoupling capacitor should be placed closer to the chip so that it can reduce the parasitic voltage droop at the switching transition.

- The second step is to remove excessive IR drops which we do by reducing the wire size. However dynamic voltage fluctuations may still occur even if the wire sizing is performed.

- We also need to place low inductance capacitances under packages and on packages. For this reason now capacitances have been designed within the silicon die and placing them in critical space which is known as white space. Because the more the capacitor placed near to the chip the more inductance loss will be reduced.

However, as guided by Moore's law, the power demand of the CMOS devices are ever increasing with faster clocks, smaller devices, and integration of analog and digital circuits within the same die. So these issues are more critical to make the management of voltage droops that's why the conventional techniques of controlling voltage droops are failing beyond a certain bandwidth.[2]

# <u>3. NOVEL METHOD OF REDUCING POWER</u> DROOP

# 3.1. Improved VLSI Circuit Performance Using Localized Power decoupling:

In "Improved VLSI Circuit Performance Using Localized Power decoupling [13]" paper, they proposed an advance technology for DRAM capacitor by using the decoupling strategy. In the paper they proposed a technique, in which the decoupling is provided at the CMOS level, right where the power is needed. This technology is needed for VLSI circuits due to increases the performance of the system, because power droop in silicon is a major problem in the semiconductor circuits. When semiconductor circuit operates in high frequency and as the power levels are reduced then the semiconductor devices are limiting the timing and voltage budget which is design in circuits to account for noise and also include voltage drooping due to inductive losses. Novel techniques are involved to compensate these losses at all levels including motherboard, package through out in silicon: but due to lack of available space and design constrain decoupling at die level is very limited. For all this, to solve the above mentioned problem this paper is come forward with an advance technology where they mention about a methodology to introduce decoupling right at the transistor. The crux of the concept is to use DRAM capacitors, as a local capacitance bank to deliver power to the devices right when the switching takes places.

In this paper they are concentrated only in dynamic power which is a function of clock frequency or more accurately is a function of the switching of the CMOS circuit transistor. Basically dynamic mower relates to bow many times the circuit switches in a second and the switching of a circuit is a unction of the RC time constant where the RC time constant depends on the source and drain apacitance at the driver end and the gate capacitance of the receiving end. But for the newer process is the source and drain of a transistor is in smaller dimension for which the capacitance reduces and entually also the resistance reduces which means it also reduces the RC time constant. As the RC me constant reduces the switching speed of the circuit increases which is the ultimate goal. But the aduced RC time constant causes the switching current to race quicker and resulting in a large di/dt which the faster switching speed translate into higher harmonics in the signals. In time domain

large di/dt cause the large voltage droop across any inductance as  $V_L=L*di/dt$ . For larger di/dt the inductive voltage drop increases which reduces the power supply to the IC. To reduce the voltage droop and increases the power supply they find an alternative source for the fast switching current where they used localized decoupling concept in the circuit. Through localized decoupling process they place a decoupling capacitor before the driving load where the decoupling capacitor operates either in charging mode or in discharging mode. To build the decoupling capacitor they incorporate the DRAM capacitor technology where the technology matures in the form of one transistor one capacitor configuration. The capacitors can be either in the stacked or trench configuration.

In this paper they bring a new ideology by bringing together two parallel semiconductor technologies. The capacitor technology follows the DRAM ideology and whiles the system level decoupling and die white space decoupling is not sufficient enough to support nano-dimensions transistor circuit with 10s picoseconds transition rates for which the trench and stacked capacitor model can be successfully designed right next to transistors without taking more space then the isolation transistor.

#### 3.2. Low-Cost Deep Trench Decoupling for Low-Power CMOS:

In "A Novel, Low-Cost Deep Trench Decoupling Capacitor for High-Performance, Low-Power Bulk "MOS Application [14]" paper; they represent an overview & electrical results for a novel deep trench decoupling capacitor, which is borrowed from the regular embedded DRAM trench process, but with significant process simplification by using decoupling, to provide reduction of cost and process cycle time. By using this phenomenon; capacitor can provide significant chip-level area savings, using only 1/8 silicon real estate to fabricate the same capacitance as standard planar gate wide capacitors and also the "decap" demonstrates a improvement in leakage compared to standard "lanar gate oxide capacitors. By using deep trench capacitor 10<sup>5</sup> improvements in leakage can be calized than in conventional planer decap designs.

Eductance is one of the unfortunate features in semiconductor circuit which produce noise on the wer delivery and have a detrimental impact on circuit performance. Decoupling capacitor (decaps) educe the induce noise and provide the low impedance path to ground. For higher clock speed evice more effective decoupling is needed. Decaps are planer oxide device where the Nwell is one

ite and gate is another. In decaps gate dielectric limits the amount of the charge which can obtains im planer decaps and are often found to contribute to standby leakage. In high speed circuit signs decap can account more than 10% of the total chip area. To solve the above stated problem this paper they introduced a novel decap design which utilized IBM's unique eDRAM technology d called as "DZ decaps" where the DZ decaps have a extremely high capacitance/area, very low akage/fF, and series resistances competitive with planar gate oxide decaps. In this paper they ention the fabrication process of Dz trench capacitor and its fabrication advantages. Basically Dz ench capacitor are fabricated in a similar manner to bulk eDRAM Deep Trench (DT) capacitor here the DZ capacitors share exactly the same pad films, oxide head mask used for trench efinition, lithography process, buried plate process and node dielectric formation process. After the ode dielectric process DZ capacitor module is much simpler than DT capacitor because there is no eed of resist recess and collar oxide formation for DZ capacitor and the full vertical trench surface an be used as decaps. In DZ decaps the number of polyfills and poly recess are reduced and because f this DZ decaps saves approximately 35% in process cost.

In the comparison of Dz capacitor and typical planar gate-oxide capacitor, the DZ decaps is much better than the typical planar gate-oxide capacitor because DZ decaps need 1/8 chip area to provide the same capacitance and the leakage is 5 order less than the typical planar gate-oxide capacitor means DZ decaps can offer more than 8X more capacitance/unit area and 10<sup>5</sup> reduction in leakage.

#### 3.3. A Decoupling Platform for Substrates, Sockets, and Interposers:

"A Novel Decoupling Capacitance Platform for Substrates, Sockets and Interposers [15]" paper, cy represent a technology deployed within substrates, interposers or sockets to enhance core power livery because power integrity has become a leading focus due to increasing demands of power livery networks in current and next generation computer system. This technology developed a vel integration of decoupling capacitance between the core power nets and the ground. Then haces the numerous decoupling capacitors sub-optimally placed on traditional printed circuit and (PCBs). This decoupling capacitor can lower the power supply noise and increased core power bility, permitting greater semiconductor switching frequency while reducing overall system cost. r actual system application, this technology proves it's superiority in both cost and performance to wide range of expensive and largely ineffective decoupling strategies. :

.....

\_\_\_\_\_

<u>\_\_\_\_</u>

In semiconductor circuits the current quest for data transmission at 10 Gbps and is hindered by instability in core voltage of supplying semiconductor beyond 10 Gbps and this problem will be more pronounced with shrinking lithography, increased switching speeds and greater power requirements. Core voltage "design for stability" has been a compartmentalized endeavor due to inadequate communication among the chip, package and board designers and also lack of system co-design combine to result in suboptimal performance, including bit-error rate, device malfunction, increased noise coupling and lower semiconductor yield. In semiconductor chips system designer restored to exotic "fixes" but unfortunately these "fixes" are inadequate because they are an after though rather than a fore though, to the system architecture design.

In today's system maintain stable core voltage and suppressing switching noise on power supply are two intimately related problems and can be solved by reducing the impedance seen by the power delivery system by providing effectively decoupling capacitance. The traditional approach to core decoupling has been to endow the PCB, substrate and die with more decoupling capacitance. If in a system hundreds or thousands of discrete decoupling capacitors are present then in practical level they are extremely wasteful these capacitors are not place near to the required part (which needs the voltage to operate properly). Due to the increase bus length and remote voltage regulator module location which introduces loss and inductance the system suffers unnecessarily. To compensate this problem they add High-capacitance interdigitated capacitors (IDCs) directly to the substrate or in PCB. This phenomenon increases the cost but for better performance the additional coat can be neglected. Incentives for a more novel, root-level solution drove the development of this new decoupling platform that integrates discrete or custom capacitance into the voltage core much closer to the die. The first feasible implementation of this solution (named as CapCor) is within a socket and provides substrate solder-attach on top and PCB solder-attach on the bottom. Viewed from a system-wide perspective, if a decoupling capacitor is added under the substrate then it is more effective than on the PCB which render hundreds of PCB decoupling capacitors redundant and reduce the total system cost. As hundreds of PCB decoupling capacitors eliminate means their supporting pads, vias and traces also eliminates which basically reduce the resistance and inductance and improve the electrical signal performance. In this new and novel configuration decoupling capacitance is integrated inside the interposer between power and ground pins where the design involves direct solder of discrete caps to the power and ground pins. In microprocessor high switching speed requires highly stable power. In this new process as the decoupling capacitor is

place near to the substrate, so it has lower parasitic component means lower power droop means highly stable power.

In this paper they presented a novel decoupling technology demonstrated to improve power delivery, suppress transient noise on the power system and stabilized the core voltage and also showed that CapCore is a superior alternative to hundreds of PCB decoupling capacitors, at the same time delivering lower power impedance which substantially reduce both the PCB complexity and total cost.

# 4. HIGH-K DIELECTRIC CONSTANT

ligh-*K* materials are dielectric material with high permittivity constant ( $\varepsilon_r$  or K). Recently high-*K* material have received wide acceptability for various applications including gate dielectrics, high loarge-storage capacitor and electro active materials [16][17][18]. The implementation of high-k gate dielectrics has allowed further miniaturization of microelectronic components, often referred to as extending Moore's Law. High-*K* materials with high dielectric constant and low dielectric loss are imperative for real applications of embedded passives, specifically capacitor to provide the size reduction and performance enhancement of many microelectronic systems [19][20].

#### 4.1. Why Need High-K?

To allow the advancement of semiconductor performance in integrated circuits, it appears likely that dielectrics other than SiO<sub>2</sub> will be required. The problem is that an optimal replacement gate dielectric for SiO<sub>2</sub> has to be found which can be used in applications requiring thickness of  $10^{\circ}$ A in a layer. At this thickness, quantum mechanical electron tunneling is prevalent, and leakage currents cannot be maintained below the proposed maximum limit of 1 A/cm<sup>2</sup> (for high performance processors) [21][22][23]. To maintain the correct transistor operation, a specific level of capacitance density is required in this small gate capacitor. This limitation appears to be of theoretical origin (i.e., unable to be relieved by continued process improvement), thus the solution demands the introduction of a new higher permittivity gate dielectric composition, or possibly a transistor offering an alternative architecture. For the improved transistor operations may only be achieved in the presence of metallic gate electrodes (highly doped poly-Si is currently in use) which will not become depleted under bias [24]. Moreover, new and improved methods and instrumentation must be developed for accurate device and process characterization. With these reduced dimensions, and the influence of the size of contaminant particles, leads to device failure. In these failures, the contaminant size fall below diameters that can be detected optically, a method currently used for contaminant particle detection [25].

In our project we develop a decoupling capacitor using High-K material. We show in this paper by using high permittivity and low loss tangent high-K material we get much better decoupling capacitance for better performance in power analysis grid. Ideally, the larger dielectric constant (K)

ill allow the thickness to be increased such that a tolerable level of tunneling leakage can be aintained. Though replacing  $SiO_2$  with any dielectric having K>4 would be theoretically itisfactory, the possibility of higher leakage must be considered. So to avoid this problem we onsider high permittivity of high-K material.

#### 4.2. High-K Dielectrics:

rom a dielectric property point of view, dielectric constant and dielectric loss are the two most nportant parameters that dictate the performance of a candidate material for embedded capacitors. This dielectrics with a high dielectric constant are very attractive for improving the decoupling berformance. To accurately estimate the performance of thin high-K dielectrics, the frequency lependent dielectric constant and the loss tangent have to be extracted [7].

n the beginning, ferroelectric ceramic materials with permanent dipole moment which gives these naterials high-K in the thousands, including BaTiO3 (barium titanate), BaSrTiO3 (barium strontium itanate), PbZrTiO3 (lead zirconate titanate) etc., have been used as dielectric materials for decoupling capacitors [30][31]. In our research we need low loss tangent and high permittivity of high-K material. So at level we select following material, Table 2 give an overview of the most commonly applied high-k dielectrics

| material                       | structure     | permittivity | l loss tangent | Reference |

|--------------------------------|---------------|--------------|----------------|-----------|

| HfO <sub>2</sub>               | amorphous MIM | 25           | 0.006          | [26]      |

| ZrO <sub>2</sub>               | amorphous MIM | 22           | 0.005          | [27]      |

| La <sub>2</sub> O <sub>3</sub> | amorphous MIM | 20           | 0.016          | 28        |

| $Y_2O_3$                       | amorphous MIM | 12           | 0.003          | [29]      |

As hafnium oxide (HfO2) or zirconium oxide (ZrO2) presents several good characteristics: *K*-value = m 15 to 35 at DC and high thermal stability in direct contact with silicon and good process = mpatibility. HfO2 and ZrO2 are promising alternatives for both MIM and MOS structures [32]. = inthanum oxides (La<sub>2</sub>O<sub>3</sub>) have high permittivity, good resistance to devitrification, and an = opreciably large band gap. The calculated permittivity of La<sub>2</sub>O<sub>3</sub> (hexagonal) is approximately 38, = sile the measured values range between 20 and 30.

# 5. SIMULATION & ANALYSIS

#### 5.1. Main Circuit:

Figure 5: simple model of Power Delivery Analysis circuit.

In Fig. 5, the equivalent model of a power delivery circuit has been designed. A typical power elivery circuit has a DC supply voltage which is supplied by a voltage regulator located on a, trinted circuit board plane. In this circuit the load is a multitude of inverters. The power path is nodeled with inductances and resistors. We have also added decoupling capacitors. Decoupling apacitors will be used to reduce the effect of parasitic inductance in power delivery networks. Decoupling capacitors are widely used to manage power supply noise [33]. The capacitor solution will be modeled at different stages of this circuits i.e at the motherbord, on the packgae and in the file. Decoupling capacitors are an effective way to reduce the impedance of power delivery systems operating at high frequencies [34]. Generally in low frequency inductance become short and by this since capacitance become charged. In the high frequency inductance operates and voltage droop cross L is increased. The total sum value of L increase which affects circuit performance. So we essent a decoupling capacitor provides the storage charge to compensate for voltage drop due to cover. The decoupling capacitor provides the storage charge to compensate for voltage drop due to inductance. Each capacitance is modeled with the parasitic resistance(ESR) and inductance(ESL) which is series with the capacitance.

Ve use the following value for the equivalent parameter in the microprocessor chip power delivery stem which is given in Table 3.

| rable 5, the value we used for the equivalent parameter than and encore |              |                    |            |             |  |  |

|-------------------------------------------------------------------------|--------------|--------------------|------------|-------------|--|--|

| Equivalent Parameter                                                    | Mother Board | Socket             | Package    | Die         |  |  |

| Resistance (R)                                                          | 0.00150hm    | 0.0050 <b>•</b> hm | 0.00050ohm | 0.000150ohm |  |  |

| Inductance (L)                                                          | 1.0nH        | 1.0nH              | 0.20nH     | 0.10nH      |  |  |

Table 3: The value we used for the equivalent parameter in main circuit

$\sqrt{c}$  also use decoupling capacitor in the power delivery system where the value we use for the quivalent capacitor model is given in Table 4.

| Equivalent Capacitor Parameter        | Mother Board           | Socket    | Package               | Die           |

|---------------------------------------|------------------------|-----------|-----------------------|---------------|

| Equivalent Series Resistance (ESR)    | <sup>F</sup> 0.0015Ohm | 0.0005Ohm | 0.0015Ohm             | ESR!**        |

| Capacitor (C)                         | r 100uF                | ;         | 100pF                 | 0.1792pF      |

| Parallel Resistance (R <sub>p</sub> ) | 5000mOhm               | 5000mOhm  | <sup>†</sup> 5000mOhm | $R_{P}I^{**}$ |

| Equivalent Series Inductance (ESL)    | 0.1nH                  | 0.2nH     | 0.2nH                 | ESL1**        |

Table 4: The value we used for the equivalent capacitor parameter

\*\*ESR1,ESL1,R<sub>P</sub>1 small and incignificant effect.

#### 5.2. ESL & ESR:

There are various design issues which affect the power distribution impedance. It has already been demonstrated that the power distribution impedance for a modern computer must be kept low and that over a large frequency range [35] for improved product performance. Power distribution system noise affects computer product timing performance. In high frequency reducing power distribution moise is with decoupling capacitors.

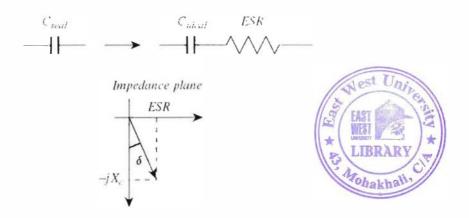

apacitor ESR determines the number of capacitors required to achieve certain target impedance at a carticular frequency and is therefore an important design parameter. ESR of a capacitor of baramount importance is within power supply design for both switching and linear power supplies. The equivalent series resistance, ESR shown in Fig. 6 plays a major part in the performance of the creuit as a whole.

#### Figure 6 : The Equivalent Series Resistance, ESR associated with a capacitor

apacitors with high values of ESR will naturally need to dissipate power as heat. It is found that hen the temperature of a capacitor rises, then generally the ESR increases, although in a non-linear shion. Increasing frequency also has a similar effect. As the dielectric thickness increases so does e ESR. As the plate area increases, the ESR will go down if the plate thickness remains the same.

SL (Equivalent Series Inductance) shown in Fig. 7 is pretty much caused by the inductance of the ectrodes and leads. The ESL of a capacitor sets the limiting factor of how well (or fast) a capacitor an de-couple noise off a power bus. The ESL of a capacitor also sets the resonate-point of a apacitor. Because the inductance appears in series with the capacitor, they form a tank circuit. The .SL is defined by the size of current loop of power circuit. The bigger the current loop the greater ne ESL inductance. By placing the capacitance closer to the CMOS, we can see a significant eduction in inductance.

Figure 7 : Capacitor equivalent circuit

#### 5.3. Why & where to place Decoupling Capacitor:

Tapacitance between power and ground distribution networks, referred to as decoupling capacitors or decaps, acts as local charge storage and is helpful in mitigating the voltage drop at supply points. The manage power supply noise decoupling capacitors are widely used. An effective way to reduce the impedance of power delivery systems operating at high frequencies are decoupling capacitors.

Figure 8: Plot frequency vs. impedance

$$Z = R + f_{(i)}L + \frac{1}{j_{(i)}C}$$

.....(i)

From Fig. 8 we see that before the point 'A' has low frequencies, where value of inductance is low compare to capacitor. Eventually at a low frequency the value of impedance is high. Generally with the frequency increases capacitance value will decreases at a point 'A' will come where the value of inductance and capacitance cancel out each other, only resistance value remains. After point 'A' as the frequency increases the capacitance decreases but inductance increases which increase the impedance. So total impedance is increase by L and R when power delivery systems run in high frequency and system performance is decreased. To reduce voltage drop of system we want place decoupling capacitance near to the chip because if place it far from the chip the inductance between circuits and decap will increase. For away from the chip, IR loss and  $L\frac{di}{dt}$  loss are increased.

5.4. Inductive drop -  $L_{dt}^{di}$ loss:

In a high frequency RC time constant is decrease and switching current is quicker that cause large  $L\frac{di}{dt}$  is increased. Therefore, the circuit will have large  $L\frac{di}{dt}$  voltage drop across any inductance  $V = L\frac{di}{dt}$ .

Figure 9 : Power Delivery Analysis circuit

In the power delivery circuit in Fig. 9 we also have resistive drop which is independent of the rate of change (i.e. switching). The total voltage drop in terms of inductance and resistance effect of notherboard, package, socket and silicon [36].

$$V_{dt} \left( Ln \frac{dt}{dt} - Rn \right) - \left( Lp \frac{dt}{dt} - Rp \right) - \left( Ls \frac{dt}{dt} - Rs \right)$$

expressing total voltage drop as the sum of inductance and resistance component,

$$V_{dr} = \sum (Ln \frac{di}{dt} - IRn)$$

So the voltage available in the circuit is

$$V_{\rm eff} = V_{\rm dd^+} V_{\rm dd}$$

Modern high performance microprocessors due to their growth in power consumption and switching speeds the  $\frac{d_1}{d_2}$  effects are becoming a growing concern. Fast switching current may cause large  $\frac{d_2}{d_2}$  and nereasing inductive drop which reduces the power rail voltage to drop. The effective power supply  $V_{eff}$  is shared across the large of component in the silicon through a network of power and ground rails. Here the circuit performance and activities of transistors are affected when voltage droop accelerates. So  $(V_{eff})$  must be minimized to improve circuit performance. We added decoupling rapacitors to counteract the  $\frac{d_1}{d_2}$  variations in the voltage. It is necessary to model accurately the inductance and capacitance of the package and chip and analyze the grid with such models, as otherwise the amount of decoupling to be added might be underestimated or overestimated. Also it is necessary to maintain the efficiency of the analysis even when including these detailed models.

5.5. Reduce Path Inductance L:

Figure 10 : Placement of decoupling capacitance.

In Fig. 10 is shown a simple model of Chip with a 1.5 DC voltage supply form DC-to-DC regulator. The power transmission buss line shown in Fig.6 has inductance and resistance. If this system runs at high frequency then inductive impedance will increase. Although the resistance is quite small, the inductance voltage drop will be significant. To compensate the impact of inductance in every step of the circuit, we need to add decoupling capacitance appropriately. Let assume we want to place decoupling caps in two white area of the chip. If we place decaps in 'position 1' the value of loop inductance is much higher than the 'position 2'.So to avoid loop inductance we need to place decaps mear the chips and minimize IR loss and  $L_{dx}^{di}$  loss.

#### 5.6. White Area:

In a semiconductor device the unused blank space (those areas not occupied by the circuit elements) refers as a white space or white area. In the modern day the size of chip going to very small so, we need to use redundant space effectively. We design decoupling capacitors in the semiconductor device white area to reduce the voltage droop. Traditionally Decoupling capacitors have been allocated into the white space available on the die based on an unsystematic or adhoe approach [37],[38], as shown in Fig. 11. As a result, the power supply voltage drops below the minimum tolerable level for remote blocks, thus affecting circuit performance. The size of an on-chip decoupling capacitor, however, is directly proportional to the area occupied by the capacitor and can require a significant portion of the on-chip area. As described in [39], maximum parasitic impedance between the decoupling capacitor and the current load (or power source) exists at which the decoupling capacitor is effective. Alternatively, to be effective, an on-chip decoupling capacitor should be placed to ensure that both the power supply and the current load are located inside the appropriate effective radius [39].

#### 5.7. Description on ADS:

In this project our major tools was ADS. We used two part from this tools these are momentum part and schematic part. In the schematic tools we were develop a power delivery analysis circuit and we use momentum tools to design a capacitance.

Momentum is an electromagnetic simulator which is used to evaluate and design modern communications systems products. Momentum can computes S-parameters for general planar

circuits, including micro strip, slot line, strip line, coplanar waveguide, and other topologies. Momentum tools use to simulate multilayer RF/microwave printed circuit boards, hybrids, multichip modules, and integrated circuits. The main things to use momentum tools is it can predict the performance of high-frequency circuit boards, antennas, and ICs. The major benefit of this is that it can simulate when a circuit model range is exceeded or the model does not exist, it can identify parasitic coupling between components, it can analysis and verification to design automation of circuit performance and it can visualize current flow and 3-dimensional displays of far-field radiation. The major features of this tool have to fit frequency sampling for fast, accurate, simulation results. To achieve performance specifications of a design the optimization tools can change geometric dimensions. It also has comprehensive data display tools for viewing results and equation and expression capability for performing calculations on simulated data.

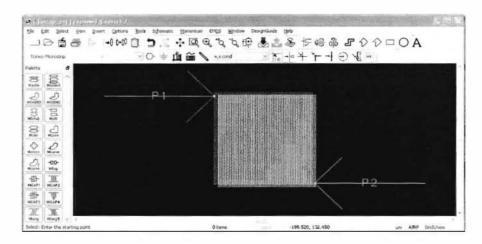

Figure 12: Momentum window of ADS

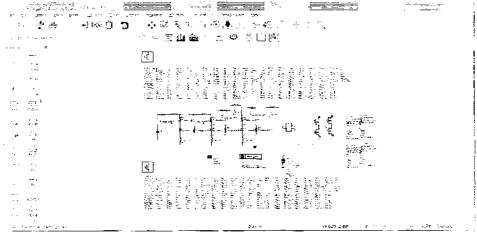

Fig.12 shows the momentum window of ADS while designing the capacitor. In the momentum we design capacitor for different type of High-K material. After design this capacitance we use **Component** option of momentum then we selected create/update and update design capacitance in the component library. After update component we use this capacitance in schematic window to simulate power delivery circuit. In Fig.13 represent the schematic window of ADS.

Figure 13 : Schematic window of ADS

We used BSIM4 transistor models both for NMOS and PMOS transistors. Designing capacitor was attached to the source node of two inverters connected back to back, each driving another inverter, to simulate a capacitive load. The model consisted of a motherboard, package, and a socket. Adequate decoupling was placed on the system, at the motherboard and package.

#### 5.8. Result & Calculation:

A simulation analysis has been done to demonstrate the advantage of local decoupling technology. It also assumes that the capacitor will be shared by about 4 back to back CMOS invertors. We design capacitance using the momentum tool from ADS. To design the capacitance the high-k material that we have used are shown in Table 5.

| Material Name                            | Dielectric | Loss tange |

|------------------------------------------|------------|------------|

| Hafnium Oxide (HfO <sub>2</sub> )        | 25         | 0.006      |

| Lanthanum Oxide ( $\overline{La_2O_3}$ ) | 20         | 0.016      |

| Yttrium Oxide( $Y_2O_3$ )                | 12         | 0.003      |

Table 5: High-k materials with dielectric constant and loss tangent.

We use 0.179pf capacitance for different analysis. Most important thing is thickness of the capacitance. If the thickness of the decoupling capacitance is very small then it does not affect on the circuit to minimize the droop. Consider these entire things we are assuming that thickness of

$IfO_2 = 0.1 \mu m$  and calculate other high-k material thickness to make the same capacitance for these naterials. Using this thickness in capacitor model then we get minimum droop for  $IIfO_2$ .

#### 5.8.1. Calculation To Make The Capacitance Same:

for HtO<sub>2</sub>, loss tangent=0.006 and permittivity=25.

Area of capacitnace, A=  $90\mu$ m $\times 90\mu$ m  $\cdot 8100 \mu$ m<sup>2</sup>

Eq. 3.85  $\times$  10  $^{-18}$  F/  $\mu m$

Capacitance of HfO<sub>2</sub>,  $C = C r \in c \frac{c}{c} \frac{2\pi \sqrt{c} \sec 10^{-13} \times \sec 0}{c_1} = 0.1792 \text{pF}$

Now to make same capacitance we need to find other high-k material thickness. For La<sub>2</sub>O<sub>3</sub>, loss tangent is 0.016 and  $\varepsilon r = 20$ . So I asume that HfO<sub>2</sub> ( $\varepsilon r = 25$ , thickness=0.1 µm) is okay for minimum droop. To keep the same value of capcitance, thickness of La<sub>2</sub>O<sub>3</sub> is  $= \frac{0.4 \times 20}{25} = 0.08$  µm and

Capacitance is  $C = \frac{2C \times 2.65 \times 10^{-15} \times 6100}{2.06} = 0.1792 pF$

Similarly, For Y<sub>2</sub>O<sub>3</sub> ,losstangent=0.003 and  $\varepsilon_r = 12$ . So thickness of Y<sub>2</sub>O<sub>3</sub>,  $\frac{\varepsilon \varepsilon (1) \cdot 12}{\varepsilon \varepsilon} = 0.048 \ \mu m$  and Cpacitance is C =  $\frac{12}{\varepsilon} \frac{\varepsilon \varepsilon \varepsilon > 16^{-13} \times \varepsilon (\alpha \varepsilon)}{\varepsilon \varepsilon \varepsilon \varepsilon} = 0.1792 \text{pF}$

In existing material SiO<sub>2</sub> is used to make the capacitance but there are some limitation in this material layer. The main cause is Si material have some limit of its thickness. We cannot make it too much thin. To make same capacitance of SiO<sub>2</sub> the calculated thickness is 0.00156  $\mu$ m, which is too small for Cr = 3.9. To avoid complex simulation we assumed the thickness of the SiO<sub>2</sub> is 0.01  $\mu$ m.

#### 5.9. Simulation Result:

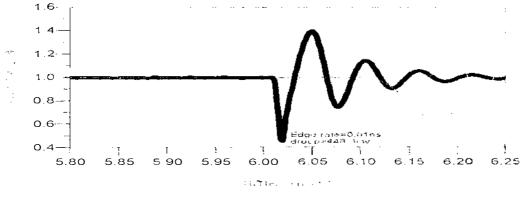

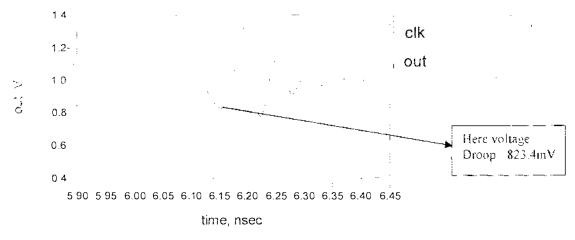

In the power delivery circuit shown in Fig. 5, we observe voltage droop before adding capacitance which is shown in Fig.14.

Figure 14 : Without decoupling capacitance voltage droop

om this Fig. we see that for lower edge(0.1ns) rate the voltage droop is 823.4mV and for the gher edge rate(0.01ns) the voltage droop is 448.3mV. So we can say that the voltage droop will crease with the increase of edge rate.

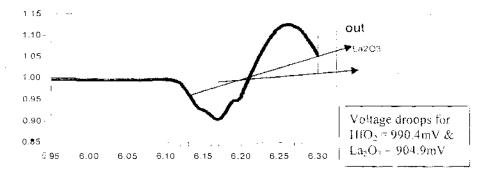

ow we want to show the improvement of the voltage droop after placing our designed capacitor oser to the CMOS circuit. The plot we got in after simulating in ADS is given Fig. 15.

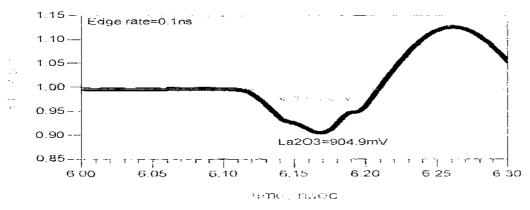

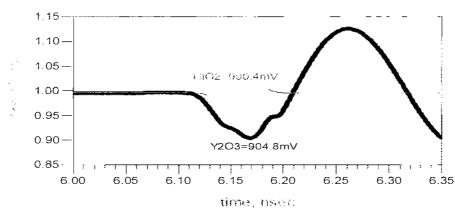

Figure 15: Showing voltage droop for HfO2 and La2O3 at 0.1ns edge rate

ere in Fig.15 shows the voltage droop for  $HfO_2$  and  $La_2O_3$  when rise time = fall time that means lige rate is 0.1ns. From this figure we can say that the voltage droop is significantly changed after acing decoupling capacitor.  $HfO_2$  has loss tangent value= 0.006 and  $La_2O_3$  has loss tangent 0.016 between them  $HfO_2$  has the lower loss tangent than the  $La_2O_3$ . The figure shows that the voltage roop for  $HfO_2$  (990.4mV which is closer to 1 in fig.15) is much lower than  $La_2O_3$  (904.9mV). So e can say that high-k material with low loss tangent can improved the voltage droop more gnificantly than higher loss tangent. In conclusion we want to say that loss tangent is a big factor to eate impact on reducing the voltage droop. 22

Ņ

18.

-

Now if we want to determine the voltage droop considering high-k material with respect to the  $SiO_2$  for the 0.1ns edge rate which simulation result is shown in Fig. 16.

Figure 16: Simulation result which shows voltage droop for SiO<sub>2</sub>, HfO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub> at 0.1ns edge rate

Here for SiO<sub>2</sub> the simulation result shows the voltage droop= 823.2mV which is much bigger than high-k material. Also without decoupling capacitor we got voltage droop = 823.4mV where after placing SiO<sub>2</sub> material decoupling capacitor voltage droop is 823.2mV so with or without capacitor in a system is the same matter for SiO<sub>2</sub>.

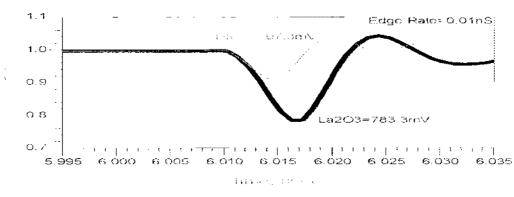

Again we did the same simulation but now we changed the edge rate which is 0.01ns that means we increased the frequency. In this situation the changed in voltage we got is shown in Fig. 17.

Figure 17: Showing voltage droop for HfO2 and La2O3 at 0.01ns edge rate

From Fig. 17 we can that voltage droop is increased, nevertheless, the low tangent material  $HfO_2$  (voltage droop of 907.3mV) gives better performance than the higher loss tangent material  $La_2O_3$  (783.3mV). In this case with edge of 0.01ns, as shown in Fig. 17, we find that without decoupling capacitor the voltage droop was 448.3mV where after placing our designed capacitor the voltage droop is significantly reduced. Now if we want to see for 0.01ns edge rate what happens with the voltage droop by using capacitors made of SiO<sub>2</sub>. The simulation result is shown in Fig. 18.

Figure 18: Simulation result which shows voltage droop for SiO<sub>2</sub>, HfO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub> at 0.01ns edge rate

In this condition again we can say that by using  $SiO_2$  material with or without placing decoupling capacitor is the same thing. Because without capacitor voltage droop was 448.3mV after placing  $SiO_2$  decoupling capacitor it shows voltage droop is 489.9 mV which is not much improved.

During our project period we worked with another high-k material which is Yttrium Oxide ( $Y_2O_3$ ). It has loss tangent =0.003 which is lower than HfO<sub>2</sub>. But the dielectric constant for this material is 12 where HfO<sub>2</sub> has 25. We take the equivalent oxide thickness for HfO<sub>2</sub> is 0.1um to make the same capacitance for both HfO<sub>2</sub> and  $Y_2O_3$ , the thickness for  $Y_2O_3$  becomes 0.048um. As a result although it has a lower loss tangent than HfO<sub>2</sub> but the voltage droop for  $Y_2O_3$  is not improved better than the HfO<sub>2</sub>. The simulation result is shown in Fig. 19.

Figure 19: Showing voltage droop for HfO<sub>2</sub> and Y<sub>2</sub>O<sub>3</sub>

So we can say that the oxide thickness is also a matter that affects the voltage droop, even though the material has the lower low tangent.

# 6. PROPOSED CAPACITOR COMPONENTS

From the previous chapter we already know about the voltage droop and its effect on microprocessor power delivery system. So the main objective of ours is to reduce the voltage droops and decoupling capacitor is one of the solutions to oppose the voltage droops. In our thesis we design few capacitor models using high-k material with low loss tangent and compare those with SiO<sub>2</sub>.

#### 6.1. Why We Use High-K Material In Designing Capacitor:

Over 40 years ago, since the introduction of the metal-oxide-semiconductor (MOS) system the SiO2 gate oxide has been serving as the key enabling material in scaling silicon CM $\bullet$ S technology. As we already know that to reduce cost, maintaining low power consumption and increasing performance devices are scaling day by day so we need to scale down the SiO2 gate oxide. However continued SiO2 gate oxide scaling is becoming difficult since (a) the gate oxide leakage is increasing with decreasing SiO2 thickness and (b) SiO2 is running out of atoms for further scaling.[40]

When devices scale and need high capacitance then the area occupied by the capacitor must scale in order to obtain a small cell size. To achieve high capacitance, the equivalent oxide thickness must be 1nm or lower. So below 90nm technology node replacing SiO2, high-k dielectric will allow the achieving of  $t_{ox}$  (equivalent oxide thickness) of <1nm. [41]

The "International Technology Roadmap for Semiconductors" published in 2008, predicts gate oxide thicknesses for the future devices which is given in Table 6.

| Year                              |                   | 2017 2018 |     |     |     |     |

|-----------------------------------|-------------------|-----------|-----|-----|-----|-----|

| Equivalent oxide thickness tex(nm | 1.1 <u>1.1</u> (r | <u> </u>  | 0.9 | 0.9 | 0.8 | 0.8 |

Table 6: The data for equivalent oxide thickness for future technology given by ITRS

So the "International Technology Roadmap for Semiconductors" predicts gate oxide thicknesses cannot be achieved by using  $SiO_2$  that's why high-k gate dielectrics and gate electrodes will be required for the future application.

Decoupling capacitors need to be placed close to the chip to reduce the voltage droop. However, in our project we want to show that at high frequency loss tangent is another factor that reduces the

### Undergraduate Thesis

effectiveness of the capacitance, despite being close to the circuit. As a result the effectiveness of the decoupling capacitor for reducing voltage droop is reduced due to loss tangent of capacitor dielectric. Thus the designed circuits fail to provide its desired performance at high frequency. So first we need to know about loss tangent and how it affects on the effectiveness of capacitance.

## 6.2. What Is Loss Tangent?

In conductive materials, currents are formed by the motion of free electrons or holes under the influence of an electric field. The relation is  $J=\sigma E$ , where  $\sigma$  is the material conductivity. For finite conductivity, resistive heating of the material causes wave power losses. We need to understand the complex permittivity as it relates to the conductivity. Thus the permittivity becomes complex, and from Maxwell's equation we know,

$$\nabla \times H = J - \frac{\partial D}{\partial t} = \sigma E - f \omega \varepsilon E \qquad (1)$$

$$\nabla \times H = \sigma E - f \omega (\varepsilon' - f \varepsilon'') E \qquad (2)$$

where  $\varepsilon = \varepsilon + j\varepsilon$ ;  $\varepsilon = -\text{real or lossless part of } \varepsilon$  and  $\varepsilon'' = \text{imaginary or lossy part of } \varepsilon$ .

$$\nabla \times H = [(\sigma - \omega \varepsilon'') - j\omega \varepsilon']E$$

$$\nabla \times H = (\sigma' - j\omega \varepsilon')E$$

(3)

where  $\sigma^{\dagger} = \sigma^{\dagger} - \omega \varepsilon^{\dagger}^{\dagger} =$  equivalent conductance.

It is clear that  $\varepsilon^{\prime\prime}$  the imaginary part of  $\varepsilon$  is involved in a frequency-dependent term  $\omega \varepsilon^{\prime\prime}$  with the dimension of conductance. For de,  $\omega = 0$  and therefore  $\omega \varepsilon^{\prime\prime} - 0$  so power loss is small in a good dielectric conductance for which  $\sigma$  is small. However at high frequency  $\omega$  is very large so losses can become larger as  $\omega \varepsilon^{\prime\prime}$  becomes significant. The sum of  $\sigma$  and  $\omega \varepsilon^{\prime\prime}$  constitutes what may be the called the equivalent conductivity  $\sigma'$ . [42]

Now the two terms of the right hand side of equation (3) are conduction current density,  $J\sigma s = \sigma E$ and displacement current density  $Jds = J\omega \varepsilon' E$ . If we take the ratio of conduction current density displacement current density magnitude then we got.

$$\frac{jzz}{jzz} = \frac{z}{z} = \frac{z}{j\omega z^{\prime}}.....(4)$$

These two vectors point in the same direction in space, but they are 90° out of phase in time. The displacement current density leads conduction current density by 90°, just as the current through a

#### ndergraduate Thesis

pacitor leads the current through a resistor in parallel with it by 90° in an ordinary electric circuit.

Figure 20: Showing the power factor angle where Js is leads E to determine loss tangent.

The angle [] is identified as the angle by which the displacement density leads the total current ensity and tan [] = []. The ratio [] is called a loss tangent because it is a measure of power as in the medium. [44]

#### 6.3. Equivalent Model of a Capacitor:

'e know for a capacitor a dielectric is placed between two conductors. The lumped element model 'a capacitor is defined by a lossless ideal capacitor in series with a resistor which is known as the juivalent series resistance (ESR). The equivalent series resistance of a capacitor is shown in Fig. . The ESR actually represents the losses in the capacitor. In a low-loss capacitor the ESR is very hall, and in a lossy capacitor the ESR can be large. Basically ESR which is shown in Fig. 21 presents the loss due to both the dielectric's conduction electrons and the bound dipole relaxation actionena.

in a dielectric either the dielectric's conduction electrons or the bound dipole relaxation menomena dominates loss. For the case of the conduction electrons being the dominant loss,  $\sqrt{r} = \sqrt{r}$  where C is the lossless capacitance.

Figure 21: Equivalent model of a capacitor and its loss tangents relation.

If we represents the electrical circuit parameters as vectors in a complex plane, then capacitor's loss tangent is equal to the tangent of the angle between the capacitor's ESR vector and the negative reactive capacitive vector, as shown in the above diagram. The loss tangent is then,

$$\tan \delta = \frac{\text{ESR}}{|Xc|}$$

where  $Xc = \frac{1}{\omega c}$

=  $\omega c. \text{ESR} = \frac{\sigma}{\delta' \omega}$

As the same AC current flows through both ESR and  $X_c$ , the loss tangent is also the ratio of the resistive power loss in the ESR to the reactive power oscillating in the capacitor. For this reason, a capacitor's loss tangent is sometimes stated as its dissipation factor or the reciprocal of its quality factor Q,

$$\tan \delta = \mathbf{D}\mathbf{F} = \frac{1}{Q}$$

So we can say from the above equation that as the loss tangent,  $\delta$  decrease then the dielectric loss of the material will also be reduced.

# 6.4. The Effect of Loss Tangent on the Effectiveness of the Capacitance:

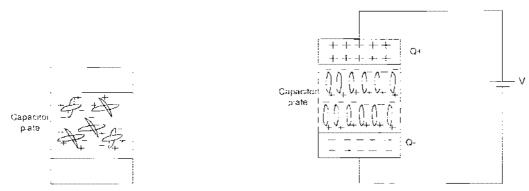

Now we want to consider how loss tangent eventually decreases the effectiveness of the capacitor. The capacitor consists of two conductors separated by dielectric medium which is shown in the Fig. 22 is shown below,

Figure 22: Initially without applied voltage V & after applied voltage V

When a dc voltage source is connected between the two conductors then charge will transfer where the positive charge will store in the upper conductor and the negative charge will store in the lower conductor. In the dielectric medium normally dipoles are randomly oriented. An applied electric field will exert a torque on the individual dipoles and tend to align these dipoles in the same direction. [45]