# An Application Specific Integrated Circuit for Optimization of Fixed Polarity Reed-Muller Expressions

Tahseen Kamal B. Sc. (CSE)

A Thesis submitted to

Department of Computer Science and Engineering Faculty of Sciences and Engineering East West University Dhaka-1212, Bangladesh

as partial fulfillment of the requirements for the degree of Master of Science in Computer Science and Engineering

April 30, 2006

This work is done with the financial support of "Imdad-Sitara Khan Foundation, Saratoga, California, USA" under AABEA Imdad-Sitara Khan Foundation Fellowship program

# **DECLARATION**

This is certified that this thesis is an original work and was done by me and it has not been submitted elsewhere for the requirement of any degree or diploma or for any other purposes except for publication.

Signature of the candidate

Johnsen Kamal

Tahseen Kamal)

# ACCEPTANCE

The Thesis entitled An Application Specific Integrated Circuit for Optimization of Fixed Polarity Reed-Muller Expressions submitted by Tahseen Kamal, I.D. No. 2005-2-96-003, to the Department of Computer Science and Engineering, East West University, Dhaka-1212, Bangladesh is accepted as satisfactory for partial fulfillment of the requirements for the degree of Master of Science (MS) in Computer Science and Engineering on April 30, 2006.

#### **BOARD OF EXAMINERS**

Lakna 30.09.06 1.-

Prof. Dr. Md. Mozammel Huq Azad Khan Dean, Faculty of Sciences and Engineering East West University Dhaka-1212, Bangladesh Chairman and Thesis Supervisor

Mr. Syed Akhter Hossain Associate Professor and Chairperson Department of Computer Science and Engineering East West University Dhaka-1212, Bangladesh

Member (Exofficio)

hrastic 30/4/06 3

Prof. Dr. A. B. M. Harun-ur Rashid Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology Dhaka-1000, Bangladesh External Member

# Acknowledgement

I would like to start by thanking the **Imdad-Sitara Khan Foundation** for giving me th opportunity to conduct the Master of Science in Computer Science and Engineering by providing fellowship.

I must thank Dr. Md. Mozammel Huq Azad Khan, for being the best guide possible to me. Without his support this thesis and my MS would never be completed.

The person who has always guided me on this path is the department Chairperson, Mr. Syed Akhter Hossain. The thesis completion is a result of his support and care which I must admit.

Mr. Shahrier Kabir, Lab In-charge, East West University, should also be thanked for his technical support.

I must also thank my family members who are and will always be with me when I am in bad time.

But above everything I would like to thank His almighty, Allah, for giving me the ability, chance, patience and stamina to complete this task successfully.

# Abstract

Classically logic functions are realized using AND-OR two-level circuits. Now a days, EXORbased logic functions have become popular, because they have some specific advantages over AND-OR realizations [Sasao 1993a]. Two-level AND-EXOR logic is one of the EXOR-based logics, which is also known as Reed-Muller logic. There are seven classes of AND-EXOR logic expressions [Sasao 1993a]. A Fixed Polarity Reed-Muller (FPRM) expression is one of them which is canonical and uses a fixed polarity for each variable. An *n*-variable function has  $2^n$ different polarity vectors; consequently, there are  $2^n$  different FPRM expressions. The expression with minimum number of products is the minimum FPRM expression. Therefore, the minimization problem of FPRM expressions is to find a polarity vector that produces an FPRM expression with minimum number of products along with corresponding coefficients. There are many software methods for FPRM minimization which are sequential in nature and require exponential execution time. In this thesis an ASIC has been developed to minimize 3-variable FPRM expressions which is parallel in nature and requires constant time. This ASIC takes the minterm coefficients of a Boolean function as input. It generates all the polarity vectors for a three variable function and determines the optimum polarity and corresponding FPRM coefficients.

# **Table of Contents**

| Chapter 1  | Introduction to AND-EXOR Expressions                               | 8  |

|------------|--------------------------------------------------------------------|----|

| Chapter 2  | Minimization of Fixed Polarity Reed-Muller Expressions             | 26 |

| Chapter 3  | Introduction to Application Specific Integrated Circuits (ASICs)   | 42 |

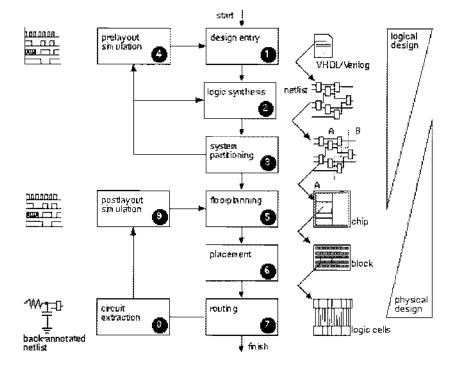

| Chapter 4  | RTL level Architecture of the developed ASIC for FPRM Minimization | 52 |

| Chapter 5  | FPGA Implementation of the developed ASIC for FPRM Minimization    | 61 |

| Chapter 6  | Discussion and Conclusion                                          | 65 |

| References |                                                                    | 66 |

# Chapter 1 Introduction to AND-EXOR Expressions

### **1.1 Introduction**

There are many ways a Boolean function can be represented. The most popular one is a *truth isble* representation. The size of the *truth table* increases exponentially with the increase of *n number of variables in the function*). Another commonly used approach is the *AND-OR* representation, also known as the *Sum-of-Products* representation which is more compact than the *truth table* representation. During the last two decades, researchers focused their eyes extensively on realizing logic functions using *EXOR-based* circuits which is more compact than the *AND-OR* representation. For example, for representing a parity function an *AND-OR* representation takes  $2^{n-1}$  product terms, whereas *AND-EXOR* representation takes *n* product terms [Sasao 1993a]. In this chapter, classification of AND-EXOR logic is presented along with detailed description of each type, their uses and advantages are also discussed [Sasao 1993a].

## 1.2 AND-EXOR Expansions of Logic Functions

The following three expansions are the basis of the AND-EXOR representation of logic functions [Sasao 1991, 1993a, 1995]:

- i. Shannon expansion

- ii. Positive Davio expansion

- iii. Negative Davio expansion

### 1.2.1 Shannon Expansion

The Shannon expansion of a logic function is defined as follows.

**Theorem 1.1 (Shannon expansion)** An arbitrary n-variable function,  $f(x_1, x_2, ..., x_n)$  can be expanded using the following expansion.

$$f(x_1, x_2, \dots, x_n) = x_i f_0 + x_i f_1$$

(1.1)

Here, we obtain  $f_0$  by putting 0 (zero) for  $x_i$  in  $f(x_1, x_2, ..., x_n)$  and  $f_1$  by putting 1 (one) for  $x_i = f(x_1, x_2, ..., x_n)$ .

Thus,

$$f_0 = f(x_1, ..., x_{i-1}, 0, x_{i+1}, ..., x_n)$$

and  $f_1 = f(x_1, ..., x_{i-1}, 1, x_{i+1}, ..., x_n)$ .

**Proof.** The theorem is proved using proof by induction. If we put  $x_i = 0$  in (1.1), we have  $(x_1, \dots, x_{i-1}, 0, x_{i+1}, \dots, x_n) = \overline{0} \cdot f_0 + 0 \cdot f_1 = f_0$ . Again, if we put  $x_i = 1$  in (1.1), we get,  $(x_1, \dots, x_{i-1}, 1, x_{i+1}, \dots, x_n) = \overline{1} \cdot f_0 + 1 \cdot f_1 = f_1$ . Thus we have the theorem. (Q.E.D)

The Shannon expansion can also be represented in the following way.

**Lemma 1.1 (Shannon expansion)** An arbitrary n-variable function  $f(x_1, x_2, ..., x_n)$  can be expanded using the following expansion.

$$(x_1, x_2, ..., x_n) = \overline{x_i} f_0 \oplus x_i f_1$$

(1.2)

where,  $f_0 = f(x_1, \dots, x_{i-1}, 0, x_{i+1}, \dots, x_n)$  and  $f_1 = f(x_1, \dots, x_{i-1}, 1, x_{i+1}, \dots, x_n)$ .

**Proof.** The sub-functions  $\overline{x_i} f_0$  and  $x_i f_1$  of (1.1) are mutually disjoint. So, + of (1.1) can be replaced by  $\oplus$ . Thus we have the lemma. (Q.E.D)

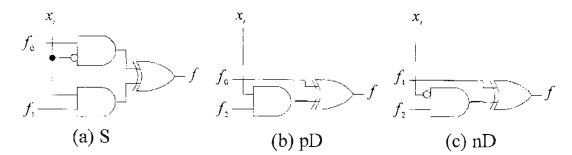

The circuit for the Shannon expansion is shown in Figure 1.1(a). In Shannon expansion, the variable  $x_i$  appears both as  $x_i$  and  $\overline{x_i}$ .

### 1.2.2 Positive Davio Expansion

The positive Davio expansion of a logic function is defined as follows.

**Theorem 1.2 (Positive Davio expansion)** An arbitrary n-variable function  $f(x_1, x_2, ..., x_n)$  can be expanded using the following expansion.

$$(1.3)$$

where  $f_0 = f(x_1, ..., x_{i+1}, 0, x_{i+1}, ..., x_n)$ ,  $f_1 = f(x_1, ..., x_{i-1}, 1, x_{i+1}, ..., x_n)$  and  $f_2 = f_0 \oplus f_1$ .

**Proof.** Since  $1 \oplus x_i = \overline{x_i}$ , from (1.2) we can write  $f(x_1, x_2, ..., x_n) = (1 \oplus x_i) f_0 \oplus x_i f_1 =$  $f_0 \oplus x_i (f_0 \oplus f_1) = f_0 \oplus x_i f_2$ . Thus we have the theorem. (Q.E.D)

The circuit for the positive Davio expansion is shown in Figure 1.1(b). In positive Davio expansion, the variable  $x_i$  appears as only  $x_i$ .

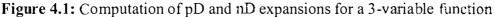

## 1.2.3 Negative Davio Expansion

The negative Davio expansion of a logic function is defined as follows.

**Theorem 1.3 (Negative Davio expansion)** An arbitrary n-variable function  $f(x_1, x_2, ..., x_n)$  can **measured** using the following expansion.

$$f_1 \otimes_{\mathbb{Z}^{n-1}} x_n = f_1 \oplus \overline{x_i} f_2$$

(1.4)

$= f(x_1, ..., x_{i-1}, 0, x_{i+1}, ..., x_n), \quad f_1 = f(x_1, ..., x_{i-1}, 1, x_{i+1}, ..., x_n) \text{ and } f_2 = f_0 \oplus f_1.$

First. Since  $1 \oplus \overline{x_i} = x_i$ , from (1.2) we can write  $f(x_1, x_2, ..., x_n) = \overline{x_i} f_0 \oplus (1 \oplus \overline{x_i}) f_1 = \frac{1}{2} \overline{x_i} f_0 \oplus f_1) = f_1 \oplus x_i f_2$ . Thus we have the theorem. (Q.E.D)

The circuit for the negative Davio expansion is shown in Figure 1.1(c). In negative Davio  $x_i$  preserves as only  $\overline{x_i}$ .

Figure 1.1 Circuits corresponding to three types of expansions.

#### **1.3 AND-EXOR Expansion Trees of Logic Functions**

$\exists ::$  applying the three expansions of (1.2), (1.3), and (1.4) for each variable of a logic function,  $d \in can$  represent a logic function using the following expansion trees [Sasao 1995].

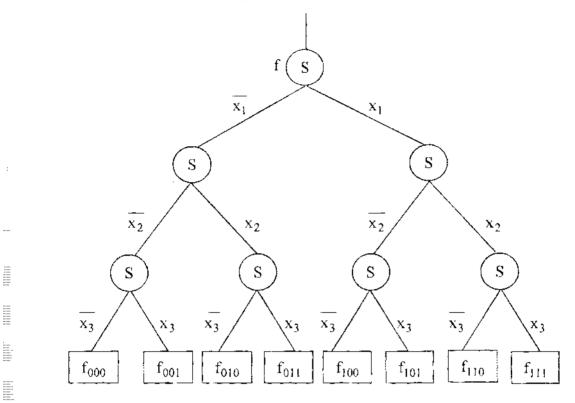

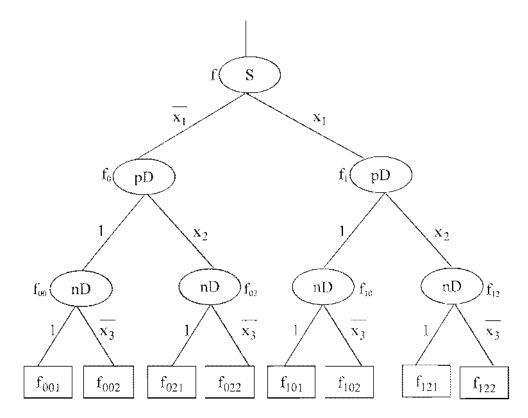

#### 1.3.1 Shannon Tree

E) applying the Shannon expansion recursively to a logic function, we can represent a logic function by a Shannon tree. Figure 1.2 shows an example of a Shannon tree for a 3-variable function f, where the symbol S denotes the Shannon expansion. The terminal nodes represent turnary constants. Each edge has a literal *(uncomplemented or complemented form of a variable)*  $f = \{x_i, \overline{x_i}\}$  of a variable as a label. A product of the literals from the root node to a terminal product term. For example, the right most path represents the product term  $t = x_2 x_3$ . The expression corresponding to this tree is,

$$= f_{000} \overline{x_1} \overline{x_2} \overline{x_3} \oplus f_{001} \overline{x_1} \overline{x_2} \overline{x_3} \oplus f_{010} \overline{x_1} \overline{x_2} \overline{x_3} \oplus f_{011} \overline{x_1} \overline{x_2} \overline{x_3} \oplus f_{01} \overline{x_1} \overline{x_2} \overline{x_3} \oplus f_{01} \overline{x_1} \overline{x_2} \overline{x_3} \oplus f_{01} \overline{x_1} \overline{x_2} \overline{x_3}$$

This expression is a canonical expression (where each product term contains all variables in the function). The products having zero coefficients disappear. Thus, the number of non-zero exerificients equals to the number of products in the expression.

Figure 1.2 A Shannon tree for 3-variable function.

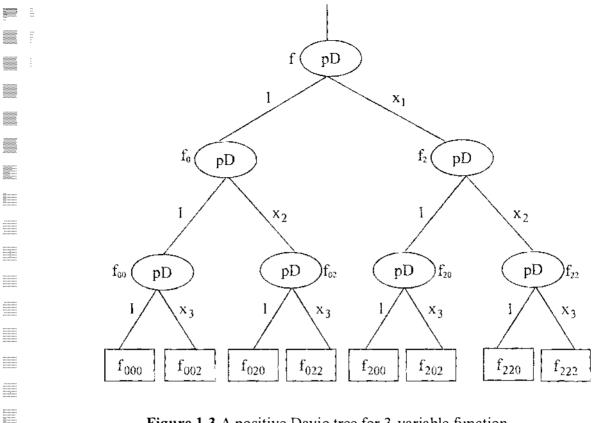

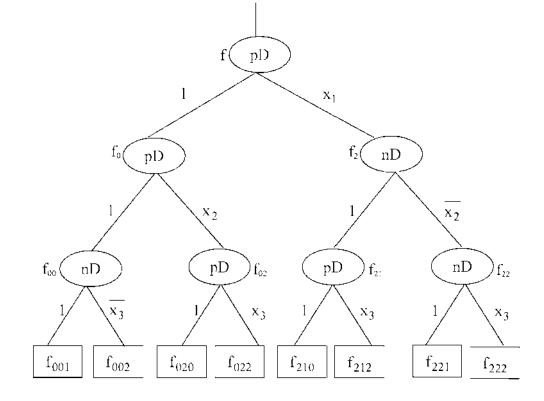

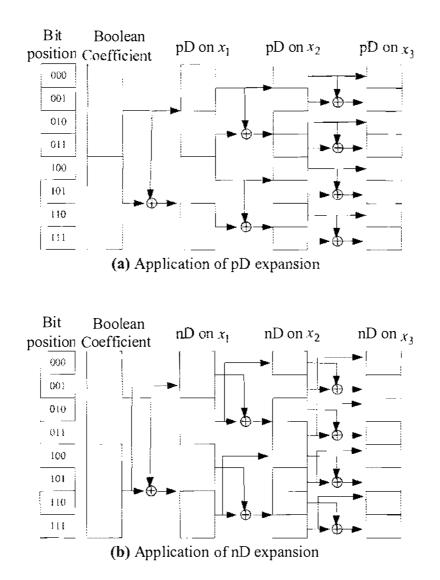

#### **1.3.2** Positive Davio Tree

.....

applying the positive Davio expansion recursively to a logic function, we can represent a scie function by a positive Davio tree. Figure 1.3 shows an example of a positive Davio tree for three-variable function f, where the symbol pD denotes the positive Davio expansion. Each size has a literal  $x_i^* \in \{1, x_i\}$  of a variable as a label. The expression corresponding to this tree

$$f_{200} = f_{000} + 1 + 1 \oplus f_{002} + 1 + x_3 \oplus f_{020} + x_2 + 1 \oplus f_{022} + x_2 + x_3 \oplus f_{200} + x_1 + 1 \oplus f_{202} + x_1 + 1 + x_3 \oplus f_{220} + x_1 + x_2 + 1 \oplus f_{222} + x_1 + x_2 + x_3$$

(1.6)

expression is a canonical expression and uses only positive (uncomplemented) literals.

Figure 1.3 A positive Davio tree for 3-variable function.

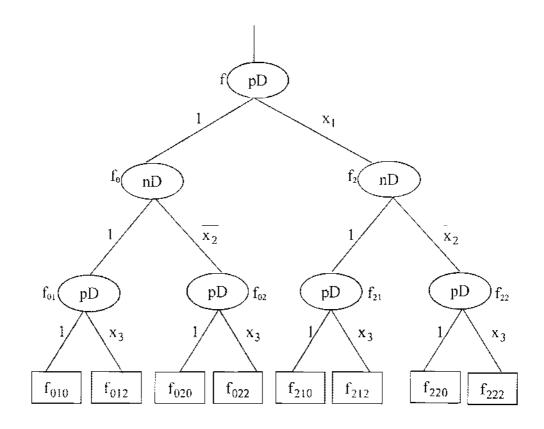

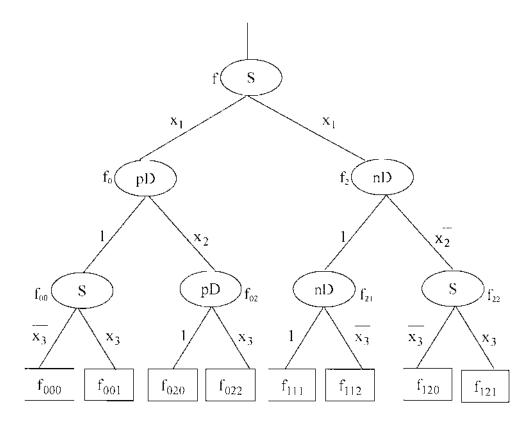

## **1.3.3 Reed-Muller Tree**

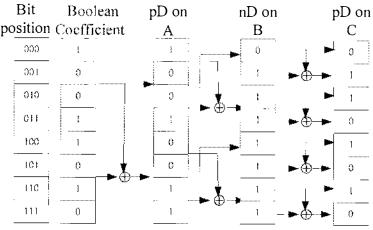

We use either the positive or the negative Davio expansion for each variable, we can represent sogic function by a Reed-Muller tree. Figure 1.4 shows an example of a Reed-Muller tree for a s-variable function f, where the symbols pD and nD denote the Positive and the Negative Davio expansions, respectively. In this tree, variable  $x_1$  and  $x_3$  use the Positive Davio expansion and ratiable  $x_2$  uses the Negative Davio expansion. The expression corresponding to this tree is,

$$= f_{010} 1 \cdot 1 \cdot 1 \oplus f_{012} 1 \cdot 1 \cdot x_3 \oplus f_{020} 1 \cdot \overline{x_2} \cdot 1 \oplus f_{022} 1 \cdot \overline{x_2} x_3 \oplus$$

$$= f_{210} x_1 \cdot 1 \cdot 1 \oplus f_{212} x_1 \cdot 1 \cdot x_3 \oplus f_{220} x_1 \overline{x_2} \cdot 1 \oplus f_{222} x_1 \overline{x_2} x_3$$

$$(1.7)$$

This expression is canonical for a given way of expansion. There are  $2^n$  different expansions for n-variable function. Different expansions will produce expressions with different number of m-variable function.

11

- .....

Figure 1.4 A Reed-Muller tree for 3-variable function.

### 1.3.4 Kronecker Tree

If we use any of the Shannon, the positive Davio and the negative Davio expansions for each matched we can represent a logic function by a Kronecker tree. Figure 1.5 shows an example of a Kronecker tree for a three-variable function f, where the symbols S, pD and nD denote the matched  $x_1$  uses the positive Davio and the negative Davio expansions, respectively. In this tree, matched  $x_1$  uses the Shannon expansion, variable  $x_2$  uses the positive Davio expansion, and matched  $x_3$  uses the negative Davio expansion. The expression corresponding to this tree is,

$$= \underbrace{f_{001} x_1 \cdot 1 \cdot 1 \oplus f_{002} x_1 \cdot 1 \cdot x_3 \oplus f_{021} x_1 \cdot x_2 \cdot 1 \oplus f_{022} x_1 \cdot x_2 x_3 \oplus f_{021} x_1 \cdot 1 \cdot x_3 \oplus f_{121} x_1 x_2 \cdot 1 \oplus f_{122} x_1 x_2 x_3 \oplus f_{121} x_1 x_2 \cdot 1 \oplus f_{122} x_1 x_2 x_3}_{(1.8)}$$

This expression is canonical for a given way of expansion. There are  $3^n$  different expansions for  $\pi$  towariable function. Different expansions will produce expressions with different number of  $\pi$  todays.

Figure 1.5 A Kronecker tree for 3-variable function.

#### 235 Pseudo Reed-Muller Tree

the use either the positive or the negative Davio expansion for each node, we can represent a signification by a pseudo Reed-Muller tree. Figure 1.6 shows an example of a pseudo Reed-Muller tree for a three-variable function f. In this tree, variable  $x_1$  uses the positive Davio expansion, variables  $x_2$  and  $x_3$  use both the positive and the negative Davio expansions. The example corresponding to this tree is

$$= \frac{1}{1 \cdot 1 \cdot 1} \oplus f_{002} 1 \cdot 1 \cdot \overline{x_3} \oplus f_{020} 1 \cdot x_2 \cdot 1 \oplus f_{022} 1 \cdot \overline{x_2} x_3 \oplus \frac{1}{1 \cdot 1 \cdot 1} \oplus f_{212} x_1 \cdot 1 \cdot x_3 \oplus f_{221} x_1 \overline{x_2} \cdot 1 \oplus f_{222} x_1 \overline{x_2} \overline{x_3}$$

(1.9)

The tree there are  $2^n - 1$  nodes for n-variable functions. So for a given order of the input  $= 2^{2^n-1}$  different expansions for n-variable functions. There are n! ordering of  $= 2^{2^n-1}$  different expansions for an *n*-variable functions. Is referred expansions will produce expressions with different number of products.

Figure 1.6 A pseudo Reed-Muller tree for 3-variable function.

#### 13 🔊 Pseudo Kronecker Tree

the use any of the Shannon, the positive Davio and the negative Davio expansions for each  $x \in x$  are can represent a logic function by a pseudo Kronecker tree. Figure 1.7 shows an  $x_1 = 1$  of a pseudo Kronecker tree for a three-variable function f. In this tree, variable  $x_1$  uses  $x_2 = 3$  mannon expansion, variable  $x_2$  uses both the positive and the negative Davio expansions,  $x_2 = 1$  mable  $x_3$  uses all of the Shannon, the positive Davio and the negative Davio expansions. The expression corresponding to this tree is

$$= \underbrace{\sum_{i=1}^{n} \overline{x_{1}} \cdot 1 \cdot \overline{x_{3}} \oplus f_{001} \overline{x_{1}} \cdot 1 \cdot x_{3} \oplus f_{020} \overline{x_{1}} x_{2} \cdot 1 \oplus f_{022} x_{1} x_{2} x_{3} \oplus f_{121} x_{1} \cdot 1 \cdot 1 \oplus f_{112} x_{1} \cdot 1 \cdot \overline{x_{3}} \oplus f_{120} x_{1} \overline{x_{2}} x_{3} \oplus f_{121} x_{1} \overline{x_{2}} x_{3}}$$

(1.10)

= 12.5 tree, there are  $2^n - 1$  nodes for *n*-variable functions. So, for a given order of the input variables, there are  $3^{2^n-1}$  different expansions for n-variable functions. There are *n*! ordering of the input variables. Therefore, there are *n*!  $3^{2^n-1}$  different expansions for an *n*-variable function. Therefore, there are *n*!  $3^{2^n-1}$  different expansions for an *n*-variable function.

Figure 1.7 A pseudo Kronecker tree for 3-variable function.

#### **AND-EXOR** Representation of Canonical Sum of Products (CSOP) Expressions

• Station tree generates an expression of the form shown in (1.5). If we replace coefficient  $f = \frac{1}{10} (1.5)$ , we have the following expression:

$$= \sum_{x_{1}} \overline{x_{1}} \overline{x_{2}} \overline{x_{3}} \oplus a_{001} x_{1} \overline{x_{2}} \overline{x_{3}} \oplus a_{010} \overline{x_{1}} \overline{x_{2}} \overline{x_{3}} \oplus a_{011} \overline{x_{1}} \overline{x_{2}} \overline{x_{3}} \oplus a_{01} \overline{x_{1}} \overline{x_{2}} \overline{x_{3}} \oplus a_{01} \overline{$$

The expression of (1.11) is a canonical expression having all minterms. This is nothing but a sum at minterm expression or CSOP expression with OR replaced by EXOR, and is known as minter EXOR-sum of products (ESOP) expression.

Example,  $f(x_1, x_2, x_3) = \overline{x_1} \overline{x_2} x_3 \oplus \overline{x_1} x_2 x_3 \oplus x_1 x_2 \overline{x_3} \oplus x_1 x_2 x_3$  is an ESOP Example,  $f(x_1, x_2, x_3) = \sum_m (1, 3, 6, 7)$ .

### **EXOR-based Representation of Disjoint Sum of Products (DSOP) Expressions**

Ligoint sum of products (DSOP) expression is defined as follows.

**Example 1.1** The disjoint sum of products (DSOP) expression for an *n*-variable function  $\exists x = x_1, \dots, x_n$  can be represented as

$$= (1.12)$$

The product terms are mutually disjoint.

The following lemma holds for the CSOP expressions.

**Lemma 1.2** The canonical sum of products (CSOP) expression is a disjoint sum of products (CSOP) expression.

**Proof.** The lemma holds, since all the minterms of a function are mutually disjoint. (Q.E.D)

**Lemma 1.3** The disjoint sum of products (DSOP) expression for an *n*-variable function  $(x_1, \dots, x_n)$  can be represented as

$$(1.13)$$

where  $\sum \oplus$  represents EXOR-sum, every instance of  $x_i^*$  in the expression can be 1,  $x_i$  or  $\overline{x_i}$ , and all the product terms are mutually disjoint.

Find f. As all the product terms of (1.12) are mutually disjoint, the + operator can be replaced  $\pi \equiv \pm$ . Thus, we have the lemma. (Q.E.D)

#### In Types of AND-EXOR Logic Expressions

There are different ways of classification of AND-EXOR logic expressions in the literature. Autocing to the classification of [Sasao 1991, 1993a, 1995], there are seven types of ACT-EXOR logic expressions. They are,

- Positive Polarity Reed-Muller (PPRM) expressions

- Fixed Polarity Reed-Muller (FPRM) expressions

- ..: Pseudo Reed-Muller (PSDRM) expressions

- Generalized Reed-Muller (GRM) expressions

- Kronecker (KRO) expressions

- v: Pseudo Kronecker (PSDKRO) expressions

- TH. Exclusive-OR Sum of Products (ESOP) expressions.

These seven classes of AND-EXOR logic expressions are discussed elaborately in the following expressions.

#### La I Positive Polarity Reed-Muller (PPRM) Expressions

20

\* positive Davio tree generates an expression of the form as shown in (1.6). If we replace method with b and subscript 2 with 1 in (1.6), we have the following expression:

$$= b_{00} \oplus b_{001} x_3 \oplus b_{010} x_2 \oplus b_{011} x_2 x_3 \oplus b_{100} x_1$$

$$= b_{101} x_1 x_3 \oplus b_{110} x_1 x_2 \oplus b_{111} x_1 x_2 x_3$$

(1.14)

Expression uses only positive literals, and is called a positive polarity Reed-Muller (PPRM) = ression. According to some authors the polarities of all the variables are 1 and according to = others the polarities are 0. This expression is a canonical expression and no minimization = clem exists.

For example,  $F(x_1, x_2, x_3) = x_1 x_2 \oplus x_2 x_3 \oplus x_1 x_3$  is a PPRM expression for the function  $(x_1, x_2, x_3) = \sum_m (3, 5, 6, 7).$

#### Ln.2 Fixed Polarity Reed-Muller (FPRM) Expressions

\* Reed-Muller tree generates an expression of the form as shown in (1.7). In (1.7) we have the  $\frac{1}{2}$  is using observations:

- For a subscript  $i \in \{0, 1\}$  of a coefficient *f*, the corresponding literal of the associated product term appears as  $x_i^* = 1$ .

- .: For a subscript i -2 of a coefficient *f*, the corresponding literal of the associated product term appears as  $x_i^* \in \{x_i, \overline{x_i}\}$  depending on the expansion used.

$\mathbf{z}$  is work, the polarity of an uncomplemented variable is represented by 0 and that of a supplemented variable by 1. The reverse polarity convention is also used in the literature, but  $\mathbf{z}$  is about this work we will follow this convention.

$\mathbb{T} = \text{replace coefficient } f \text{ with } b, \text{ subscript 1 with 0, subscript 2 with 1, and literals } x_i \text{ and } \overline{x_i}$   $\mathbb{T} = x_i^* \text{ in (1.7), we have the following expression:}$   $\mathbb{T} = b_{001} x_3^* \oplus b_{010} x_2^* \oplus b_{011} x_2^* x_3 \oplus b_{100} x_1^*$   $\mathbb{T} = b_{011} x_1^* x_3^* \oplus b_{110} x_1^* x_2^* \oplus b_{111} x_1^* x_2^* x_3^*$  (1.15)  $\mathbb{T} = x_i^* = \begin{cases} x_i & \text{if polarity of } x_i \text{ is 0} \\ |x_i^* - if \text{ polarity of } x_i \text{ is 1} \end{cases}$

recoression uses fixed polarity for a given variable and is called a fixed polarity Reed-Muller **EXA** expression. This expression is canonical for a given polarity vector of the variables. In the FPRM expression for a logic function is represented as follows:

**Example**, the FPRM expression for a 3-variable function  $f(x_1, x_2, x_3)$  with polarity vector p can be represented as,

$$= b_{000} \oplus b_{001} x_3 \oplus b_{010} \overline{x_2} \oplus b_{011} \overline{x_2} x_3 \oplus b_{100} x_1 \oplus b_{101} x_1 x_3 \oplus b_{110} x_1 \overline{x_2} \oplus b_{111} x_1 \overline{x_2} x_3$$

**Example**,  $F(x_1, x_2, x_3) = \overline{x_1 x_2} \oplus \overline{x_2 x_3} \oplus \overline{x_1 x_3}$  is an FPRM expression for the function  $x_3 = \sum_m (1, 4, 5, 7)$  with the polarity vector p = (101).

#### Seudo Reed-Muller (PSDRM) Expressions

Exercice Reed-Muller tree generates an expression of the form as shown in (1.9). This type of conversion is called a pseudo Reed-Muller (PSDRM) expression. For a given order of the input **Examples**,  $2^{2^{n-1}}$  different pseudo Reed-Muller trees exist. Different orderings of the input **new:** produce different expressions. There are *n*! different orderings of n input variables. **Example**,  $n/2^{2^n-1}$  different PSDRM expressions exist for an *n*-variable function. Different merssions will produce different number of products. An expression with minimum number of **metatts** is the minimum PSDRM expression for a given function. Therefore, the minimization set en of PSDRM expressions is to find an expression having minimum number of products. For example,  $F(x_1, x_2, x_3) = x_1 x_2 \oplus \overline{x_2} x_3 \oplus x_1 \overline{x_3}$  is a PSDRM expression for the function (1, 4, 6, 7).

### **Generalized Reed-Muller (GRM) Expressions**

Extendized Reed-Muller (GRM) expression is derived from a PPRM expression. The PPRM **constant** for a 3-variable function is represented as

$$= x_{2}, x_{3} = b_{000} \oplus b_{001} x_{3} \oplus b_{010} x_{2} \oplus b_{011} x_{2} x_{3} \oplus b_{100} x_{1} \oplus b_{101} x_{1} x_{3} \oplus b_{110} x_{1} x_{2} \oplus b_{111} x_{1} x_{2} x_{3}$$

$$(1.16)$$

**T**  $\ast$ : Heely choose the polarities of the literals in (1.16), we have the following expression.

$$= \frac{1}{2} \sum_{x_2, x_3} b_{000} \oplus b_{001} x_3^* \oplus b_{010} x_2^* \oplus b_{011} x_2^* x_3 \oplus b_{100} x_1^* \oplus b_{010} x_1^* x_3^* \oplus b_{110} x_1^* x_2^* \oplus b_{110} x_1^* x_2^* x_3^*$$

(1.17)

where every existence of  $x_i^*$  denotes either  $x_i$  or  $\overline{x_i}$ .

of expression is called generalized Reed Muller (GRM) expression. In a GRM both the positive and the negative literals may appear at the same time for a given in a GRM expression, no two products have the same set of variables. For an n-variable in a GRM expression, no two products have the same set of variables. For an n-variable in the total number of literals is  $n \cdot 2^{n-1}$ . Thus  $2^{n2^{n-1}}$  different GRM expressions exist for mable function. Different expressions will produce different number of products. An with minimum number of products is the minimum GRM expression for a given Therefore, the minimization problem of GRM expressions is to find an expression in the minimum number of products. For example,  $G(x_1, x_2, x_3) = \overline{x_1 x_2} \oplus x_2 \overline{x_3} \oplus x_1 x_3$  is a more the minimum number of  $f(x_1, x_2, x_3) = \sum_m (0, 1, 2, 5, 6, 7)$ .

#### Kronecker (K O) Expressions

**We consider the generates an expression of the form as shown in (1.8).** This type of expression and a Kronecker (KRO) expression. There are  $3^n$  different KRO expressions for an and the function. Different expressions will produce different number of products. An an expression with minimum number of products is the minimum KRO expression for a given and the function. Therefore, the minimization problem of KRO expressions is to find an expression and minimum number of products. For example,  $F(x_1, x_2, x_3) = x_1 x_2 x_3 \oplus \overline{x_1 x_2 x_3}$  is a KRO and the function  $f(x_1, x_2, x_3) = \sum_m (0, 7)$ .

#### Pseudo Kronecker (PSDK O) Expressions

Kronecker tree generates an expression of the form as shown in (1.10). This type of ession is called a pseudo Kronecker (PSDKRO) expression. For a given order of the input ess,  $3^{2^n-1}$  different pseudo Kronecker trees exist. Different orderings of the input variables different expressions. There are *n*! different orderings of *n* input variables. Therefore, different PSDKRO expressions exist for an *n*-variable function. Different expressions enduce different number of products. An expression with minimum number of products is cumum PSDKRO expression for a given function. Therefore, the minimization problem of RO expressions is to find an expression having minimum number of products. For *x*=*t*,  $F(x_1, x_2, x_3) = \overline{x_1} \oplus x_1 \overline{x_2} \oplus x_1 \overline{x_2}$  is a PSDKRO expression for the function  $f(x_1, x_2, x_3) = (x_1, x_3, x_3) = (x_1, x_3, x_3$

#### **Exclusive-OR sum of products (ESOP) Expressions**

Ξ

sive-OR sum of products (ESOP) expression is the most general class of AND-EXOR accessions and can be represented as follows:

**Exclusive-OR** sum of products (ESOP) expression for an arbitrary n-variable function  $x_1, \dots, x_n$ ) can be represented as

$$(1.18)$$

$\sum \oplus \sum \oplus$  represents EXOR-sum and each existence of  $x_i^*$  can be chosen as 1,  $x_i$  or  $x_i$

The given Boolean function. For example,  $F(x_1,x_2) = x_1 \oplus x_2 \oplus x_1 x_2 \oplus x_1 x_2$  is a ESOP expression for the function  $f(x_1,x_2) = \sum_m (0,1,2,3)$ .

#### Le Double Fixed Polarity Reed-Muller Expressions

Isss of AND-EXOR expression has been proposed in [Hirayama 2001]. It is stated that Fixed Polarity Reed-Muller (DFPRM) expressions are generalized FPRM expressions require less product terms than FPRM expressions. The definition is elaborated below.

**Example** ition 1.2 The polarity vector of a given FPRM F is denoted by v(F).  $\overline{v}(F)$  is defined as the second complement of v(F).

each polarity vector  $v_i$  denotes the polarity of the variable  $x_i$ ;  $v_i = 0$  means the positive expansion is used for the variable  $x_i$  and  $v_i = 1$  means the negative Davio expansion is used.

**Example 1.3** Let  $F_a$  and  $F_b$  be FPRMs such that  $v(F_a) = \overline{v}(F_b)$ , where we assume that the *n*-  $\overline{v} \ge v(F_a)$  is 0 without loss of generality. The EXOR combination of the two FPRMs,  $\overline{z} = \overline{z}$ , is called a *Double Fixed-Polarity Reed-Muller expression* (DFPRM) with the polarity  $\overline{v} = v(F_a)$ .

example, we have two FPRM expressions  $F_a(x_1, x_2, x_3, x_4) = x_1 \oplus \overline{x_2} \overline{x_3} x_4$  and  $F_a(x_1, x_2, x_3, x_4) = \overline{x_1} x_2 x_3 \overline{x_4} \oplus \overline{x_1} \overline{x_4}$ . Here,  $v(F_a) = [0, 1, 1, 0]$  and  $v(F_b) = [1, 0, 0, 1]$ .  $F = \overline{F_1} \oplus \overline{F_b} = x_1 \oplus \overline{x_2} \overline{x_3} x_4 \oplus \overline{x_1} \overline{x_4}$  is a DFPRM. The polarity of F is [0, 1, 1, 0].

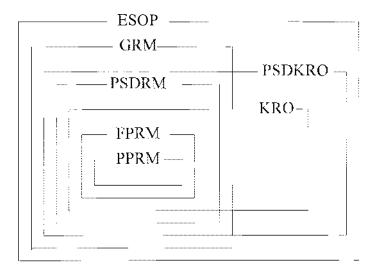

## **Relations among Various Classes of AND-EXOR Logic Expressions**

**Example and Series an**

**1.4** Suppose that PPRM, FPRM, PSDRM, GRM, KRO, PSDKRO, and ESOP denote **Content** and **Content** and

- i.  $PPRM \subset FPRM$

- ii.  $FPRM \subset PSDRM$

- iii. FPRM  $\subset$  KRO

- iv. KRO⊂ PSDKRO

- v. PSDRME  $\subset$  PSDKRO

- vi. PSDRM  $\subset$  GRM

Relations (i) to (v) are trivial and follow from the definitions. From definition, a PSDRM Sector 2 GRM and relation (vi) holds. Thus we have the theorem. (Q.E.D)

**The relations among the various classes of AND-EXOR logic expressions stated in theorem (1.4) EXAMPLE 1.8 [Sasao 1991].**

Figure 1.8 Relation among various types of AND-EXOR expressions

Telations among various classes of AND-EXOR logic expressions are discussed using the stage stange examples [Sasao 1991]:

$x_1x_2 \oplus x_2x_3 \oplus x_1x_3$  is a PPRM expression, since all the literals are positive.

$\therefore x_1 x_2 \oplus x_2 x_3 \oplus x_1 x_3$  is a FPRM expression, but not a PPRM expression, since  $x_1$  and  $x_3$  have positive literals, but  $x_2$  has negative literals.

- $x_1x_2 \oplus \overline{x_2}x_3 \oplus \overline{x_1x_3}$  is a PSDRM expression, but not a FPRM expression, since  $x_2$  and  $x_3$  have literals of both polarities.

- $x_1x_2x_3 \oplus \overline{x_1x_2x_3}$  is a KRO expression since  $x_1$ ,  $x_2$  and  $x_3$  have literals of both polarities.

- $f = \overline{x_1} \oplus x_1 x_2 \oplus x_1 \overline{x_2}$  is a PSDKRO expression, but not a KRO expression.

- $x = \overline{x_1} \oplus x_1 x_2 \oplus x_1 x_2$  is a PSDKRO expression, but not a PSDRM expression, since it contains two products of the highest degree.

- \*  $x_1 \oplus x_2 \oplus \overline{x_1 x_2}$  is a GRM expression, but not a PSDRM expression.

- :  $x_1 \oplus x_2 \oplus x_1 x_2$  is a GRM expression, but not a PSDKRO expression.

- $x_1x_2x_3 \oplus x_1x_2x_3$  is a KRO expression, but not a GRM expression, since it contains two products of the highest degree.

- $x_1 \oplus x_2 \oplus x_1 x_2 \oplus \overline{x_1 x_2}$  is an ESOP expression, but neither GRM nor PSDKRO expressions.

# Advantages of AND-EXOR Logic

EXOR logic exhibits specific advantages in the following areas [Sasao 1993a].

## Testability

SO-EXOR logic shows the following advantages in the field of testability:

- a. PLA implementation of PPRM, FPRM and GRM expressions are very easy to test [Reddy 1972, Saluja 1975, Fujiwara 1985, Sasao 1994, 1997].

- In AND-EXOR two-level networks, tests that detect all detectable struck-at faults can be generated in polynomial time of the number of the products. On the other hand, in AND-OR two-level networks, the test generation problem is not polynomial time solvable [Toida 1992].

- : AND-EXOR circuits are more amenable to efficient testing strategies than their Boolean counterpart [Mukhopadhyay 1970, Besslich 1985, Helliwell 1988, Harking 1990].

## Products Requirements

Examples with the existing minimization methods show the following advantages of  $\Delta C$ -EXOR logic in the field of products requirements:

- E For symmetric functions, ESOP expressions never require more products than SOP expressions [Rollwage 1993].

- For arithmetic functions, the number of products tends to decrease in the following order: PPRM, FPRM, SOP, KRO, PSDRM, PSDKRO, GRM and ESOP [Sasao

1991, 1993b, Debnath 1995]. Therefore, for arithmetic functions, KRO, PSD PSDKRO, GRM, and ESOP expressions require fewer products than expressions.

- c. For pseudo-randomly generated function with 2<sup>n-1</sup> true minterms, the number products tends to decrease in the following order: PPRM, FPRM, KRO, PSD PSDKRO, SOP, GRM, and ESOP [Sasao 1991, 1993a, Debnath 1995]. There for pseudo-randomly generated functions with 2<sup>n-1</sup> true minterms, GRM and E expressions require fewer products than SOP expressions.

- d. For 4-variable functions, the average number of products decreases in the feller order: FPRM, KRO, PSDRM, SOP, PSDKRO, and ESOP [Sasao 1991. 1 or Therefore, for 4-variable functions, PSDKRO and ESOP require on average products than SOPs.

- e. For 5-variable functions, the average number of products decreases in the follow order: KRO, PSDRM, PSDKRO, and ESOP [Sasao 1991, 1993a].

- f. For 6-variavble functions, an ESOP requires at most 16 products whereas a requires 32 products for realizing an arbitrary function [Sasao 1991, 1993a].

From the above discussion, it can be summarized that in general PSDKRO, GRM, and E requires fewer products than SOP.

# Synthesis and Minimization Techniques

AND-EXOR logic supports design methods, which involve algebraic techniques similatese encountered with the algebra of real numbers [Mukhopadhyay 1970, Harking 1 Davio 1978].

# VLSI Design

AND-EXOR logic circuits exhibit a modular structure which may make them suitable \$151 design [Fleisher 1983, Helliwell 1988, Green 1991].

## **Multiple-valued Logic Synthesis**

The techniques for synthesis and minimization of AND-EXOR logic extend readily matter multiple-valued logic circuits [Green 1976, 1987, Sasao 1993b].

# Application as Tool

The AND-EXOR logic expressions have the following applications as tool:

- **E** Fault of any logic circuit can be detected by verification of its Reed-Muller coefficients [Damarla 1989].

- Boolean matching can be detected using FPRM representation as a tool [Tsai 1994a].

- Symmetry of Boolean functions can be detected using FPRM expressions as a tool [Tsai 1996].

- Boolean functions can be classified using FPRM expressions as a tool [Tsai 1997].

# **Compter 2 Mainimization of Fixed Polarity Reed-Muller Expressions**

# Introduction

Finally, we consider the second seco

# Literature Review on Minimization of Fixed polarity Reed-Muller (FPRM)

Transfor FPRMs exist. We discuss some of the representative methods.

# **EXAMPLE 1** Fast exact and quasi-minimal minimization of highly testable fixed polarity **EXOR canonical networks** [Sarabi 1992]

Thapter 1 we know about the different classes of AND-EXOR expressions and their metages. Here, we will discuss about a fast exact and quasi-minimal algorithm which metages FPRM canonical networks.

meet to differentiate between the Boolean product terms and the terms in Reed-Muller forms,

"monoterm" is used for the latter.

**Efficient 2.1** A monoterm is a product term in Reed- Muller canonical (RMC) forms.

The acronym RMC is the same expression as the PPRM expressions discussed in chapter 1. The FPRM is replaced by CGRM (Consistent Generalized Reed-Muller) expressions. Fisher 1974], the problem of CGRM minimization of a switching function can be into two steps. The first step is to identify the minimal polarity and the second is to the CGRM expansion of the function with this polarity.

The disjoint cubes which represent the function [Fisher 1974, Schafer 1991, Varma 1991]. The disjoint cubes which represent the function [Fisher 1974, Schafer 1991, Varma 1991]. The the function is represented by disjoint cubes rather than minterms to reduce the manual requirements. Monoterms representing each cube are expanded and those occurring in number of cubes are retained as the ones representing the function. The fast method manual here uses the new operations of cube commonality, difference, and symmetric together with a fast Gray-code approach to realize a CGRM expansion. Before the method, the monoterms representing each cube, originally reported by [Fisher firs the case of CGRM, are given by Theorem 2.1.

**Example 1.1** The monoterms originating from a cube for the RMC expansion are all the cubes **Example their 1s** in the same literal positions as the 1s of the original cube and either "0" or "-" **Example 1.1** Here a positions of the original cube. These monoterms is referred to as monoterms **Example 1.1** The same literal positions of the original cube.

#### Table 2.1 Various operators for a single bit

| (a) Equivalence |   |   |   | (b) Cube commonality |  |   |   | (c) C | (c) Cube difference |  |   |   |   |   |

|-----------------|---|---|---|----------------------|--|---|---|-------|---------------------|--|---|---|---|---|

|                 | ≡ | 0 | 1 |                      |  | Г | 0 | 1     | _                   |  | _ | 0 | 1 | _ |

|                 | 0 | 1 | 0 |                      |  | 0 | 0 | 1     | _                   |  | 0 | £ |   | 1 |

|                 | 1 | 0 | 1 | _                    |  | 1 | 1 | 1     | Φ                   |  | 1 | e | e | Φ |

|                 | — | - |   | —                    |  | — |   | Φ     | —                   |  | — | e | Φ | e |

First, the function is represented as a set of disjoint cubes. The cubes are then operated by First, the function is represented as a set of disjoint cubes. The cubes are then operated by First, the function with the polarity of the CGRM. The symmetric difference of all these found and monoterms representing each of the resulting cubes are generated in a Grayinder. Finally, the Equivalence operation with the polarity cube is performed on each of monoterms to give the CGRM expansion. The number of the resulting monoterms can be from the *inclusion-exclusion* principle. This number is given by the following theorem:

**Derrem 2.2** Let  $C_1, C_2, ..., C_n$  be a set of *n* disjoint cubes. Let  $S_k$  denote the sum of the number **management**  $C_1, C_2, ..., C_n$  be a set of *n* disjoint cubes. Let  $S_k$  denote the sum of the number **management**  $C_1, C_2, ..., C_n$  be a set of *n* disjoint cubes. Let  $S_k$  denote the sum of the number **management**  $C_1, C_2, ..., C_n$  be a set of *n* disjoint cubes. Let  $S_k$  denote the sum of the number **management**  $C_1, C_2, ..., C_n$  be a set of *n* disjoint cubes. Let  $S_k$  denote the sum of the number **management**  $C_1, C_2, ..., C_n$  be a set of *n* disjoint cubes. The number of monoterms representing the set **management**  $C_1, C_2, ..., C_n$  be a set of *n* disjoint cubes. The number of monoterms representing the set **management**  $C_1, C_2, ..., C_n$  be a set of *n* disjoint cubes. The number of monoterms representing the set **management**  $C_1, C_2, ..., C_n$  be a set of *n* disjoint cubes. The number of monoterms representing the set **management**  $C_1, C_2, ..., C_n$  be a set of *n* disjoint cubes. The number of monoterms representing the set **management**  $C_1, C_2, ..., C_n$  be a set of *n* disjoint cubes. The number of monoterms representing the set **management**  $C_1, C_2, ..., C_n$  be a set of *n* disjoint cubes. The number of monoterms representing the set **management**  $C_1, C_2, ..., C_n$  be a set of *n* disjoint cubes. The number of monoterms representing the set **management**  $C_1, C_2, ..., C_n$  be a set of *n* disjoint cubes. The number of monoterms representing the set **management**  $C_1, C_2, ..., C_n$  be a set of *n* disjoint cubes. The number of monoterms representing the set **management**  $C_1, C_2, ..., C_n$  disjoint cubes. The number of monoterms representing the set **management**  $C_1, C_2, ..., C_n$  disjoint cubes. The number of monoterms representing the set **management**  $C_1, C_2, ..., C_n$  disjoint cubes. The number of monoterms representing the set **management**  $C_1, C_2, ..., C_n$  disjoint cubes. The number of monoterms represent  $C_1, C_2, ..., C_n$  dis the number o

$S_1 - 2S_2 + 4S_3 - 8S_4 + \dots + (-2)^{k-1}S_k + \dots + (-2)^{n-1}S_n$

the above equation,  $S_1$  denotes the number of all monoterms that are only in one cube,  $S_2$ in the number of all monoterms that are common in any two cubes, etc.

identification of the minimal polarity is an NP-hard problem, certain features of the second to reduce the required search space. Some of these features, if

the amount of search needed to find the minimal polarity without any search. Others can just the amount of search needed to find the exact solution. In the case that none of the the exist, the whole exhaustive search needs to be performed.

The number of expansion monoterms for a set of disjoint cubes is the difference between the sum of the number of monoterms representing each cube and the number of monoterms that subtracted because they occur in an even number of cubes. Both of these numbers change inferent polarities. The minimal polarity is the one which results in the optimum balance are these two numbers resulting in the least number of expansion monoterms.

These are certain features of the function that can be used to reduce the search space for sping the minimal polarity. For the case of functions that are comprised of only one cube, the minimal polarity can be found directly without any search.

**Theorem 2.3** The minimal polarities for a single cube are the polarities which match all the metals in the cube. The number of such polarities is equal to  $2^{N_{DC}}$  where  $N_{DC}$  is the number of **SE**-interals in the cube.

\*Tern a function is comprised of more than one cube, there are other features that if they exist, to the search space reduction. Theorem 4 provides one criteria for identifying a minimal multiplication of an array of disjoint cubes, using Theorem 2.2.

**Theorem 2.4** Let  $S_i^{i}$  denote the sum of  $S_i$ s of the cubes which have a value of 1 in a given minimum. Let  $S_i^{0}$  denote the sum of  $S_i$ s of the cubes which have a value of 0 in that column. Let  $E^{-iCC_i}$  denote the sum of  $S_i$ s of the cubes that have both 1s and DCs in the column, assuming me 1 has been changed to a 0. Let  $S^{0-DC_i}$  denote the sum of  $S_i$ s of the cubes that have both 0s mc DCs in the column. The corresponding minimal polarity literal for a column in the array of ms on the column in the array of ms of the cubes should be changed when set the column in the column in the array of ms of the cubes should be changed when set the cubes set the cubes should be changed when set the cubes set the cubes set the cubes set the

$$\sum_{k=1}^{k} (-2)^{k-1} S_k^1 + \sum_{k=2}^{n} (-2)^{k-1} S_k^{1-DC_*} < \frac{1}{2} \sum_{k=1}^{n} (-2)^{k-1} S_k^0 + \sum_{k=2}^{n} (-2)^{k-1} S_k^{0-DC}$$

From Theorem 2.4, it is possible to infer the following theorem:

**Theorem 2.5** For a column comprised of all 0s or all 1s, the corresponding minimal polarity steral is the same as the value in the column. (If the opposite is chosen, the number of monoterms representing the cubes would be doubled.) For a column comprised of all DC values, either 0 or 1 will be the minimal literal value.

In the Exact method of minimization, first it is checked if the function is only comprised of one rube or two. Direct solution for these cases is found using Theorems 2.3, 2.4 and 2.5. If there are more cubes involved, first Theorem 2.5 is used to identify any columns in the array of disjoint rubes for which minimal polarity literal can be found readily. All the other columns are set to the

polarity and a search for minimal polarity is performed in Gray-code order, changing one minima a time.

Then a fast heuristic approach to the minimization problem is introduced. The corresponding becaustics combine the characteristics of the overall number of monoterms and the ones subtracting, in order to identify the minimal CGRM polarity for a given array of disjoint cubes. Based on these heuristics, a priority of search for different polarities is devised and a minimization algorithm is introduced. This fast program can be used to bring more EXOR milization into the realm of logic synthesis.

### 2.2.2 Minimization of fixed-polarity AND/XOR canonical networks [Tsai 1994b]

In the paper [Tsai 1994b] the term GRM is same as the FPRM expressions discussed in chapter

Let  $f(x_1, x_2, ..., x_n)$  be a completely specified Boolean function. Each of  $x_i$ , where,  $x_i \in \{0,1\}$  is a vertex in the domain of the function. The set of vertices that the function evaluates to I is called the off-set of f. The set of vertices that the function evaluates to  $\theta$  is called the off-set of f. A conjuctor of a function f, denoted  $f_{x_i}$ , is the function derived from f when  $x_i$  is set to I. Similarly,  $f_{x_i}$  is a cofactor of f when  $x_i$  is set to  $\theta$  in f. |f| denotes the number of the on-set f is used to represent the literal of variable  $x_i$ ;  $t_i$  can be either  $x_i$  or  $\overline{x_i}$ . A vertex is a product of literals. A vertex is covered by a cube if the vertex is contained in the cube.

A Boolean difference of f with respect to a variable  $x_i$ , denoted  $f_{x_i}^B$  is defined as  $f_{x_i,...,x_i,...,x_n} \oplus f(x_1,...,x_i,...,x_n)$ . It can be computed from the formula  $f_{x_i}^B = f_{x_i} \oplus f_{\overline{x_i}}$ . The shannon expansion and the identity  $x_i = I \oplus x_i$ , we can derive,  $f = x_i f_{x_i}^B \oplus f_{\overline{x_i}}$ (2.1)

e heuristic algorithm that simultaneously generates both a

**Example** 1 polarity vector and the GRM form. To find the optimal polarity of a variable  $x_i$ , it is is included which of the expression between (2.1) or (2.2) is to be chosen. The one which have fewer cubes in the final GRM form must be chosen. This process will continue recursively reach variable and an FDD can be formed.

**Example:** The table of the second on an average for computation.

# A Genetic Algorithm for minimization of Fixed Polarity Reed-Muller

Algorithms (GAs) are often used in optimization and machine learning [Davis 1991, [Davis 1989]. One approach to minimize Fixed Polarity Reed-Muller expressions using GA [Davis 1989].

scomprised of several steps. These include representation of the problem in GA domainsection of the population, finding an object function or fitness function, setting selection working with various GA operators. For representing FPRM expressions polarity vector cosen for each variable. Thus, each element of the population corresponds to an *n*metric scenal binary vector. A population is a set of vectors. Using this binary encoding each compresents a valid solution.

= : bjective function that measures the fitness of each element used here is the number of the FPRM corresponding to the chosen polarity. This function has to be minimized to final two-level representation of the function.

This guarantees that the best element is never gets lost and thus faster convergency is

The resulting the second secon

**De CA** operators used here are *reproduction*, *crossover*, *2-time crossover*, *mutation*, *2-time*

Emposed GA works in the following steps:

Initially a random population of binary finite strings is generated and i elements are optimized by the greedy heuristic as discussed above.

The better half of the population is copied in each iteration without modification. Then the genetic operators, *reproduction* and *crossover* are applied to another  $\frac{pop}{2}$  elements. The elements are chosen according to their fitness as described above. The newly created elements are then mutated by one of the three mutation operators with a given probability.

The algorithm stops if no improvement is obtained for  $50 \cdot \log(best \_fitness)$  iterations, where *best\_fitness* denotes the fitness of the best element in the population. Finally if i > 0 the greedy algorithm is applied to the best element.

me genetic operators are iteratively applied corresponding to their probabilities.

- Reproduction is performed with a probability of 20%.

- *Crossover* and *2-time crossover* are performed with a probability of 80%.

- *Mutation, 2-time mutation* and *mutation with neighbor* are carried out on the newly generated elements with a probability of 15%.

Experimental results show that for up to 15 variables the proposed HGA gives as many as moduct terms as the exact algorithms give but require much less CPU seconds. For functions minimize the second secon

The pure GA *i.e.* the GA without application of the greedy heuristic, performs not very good,  $\frac{1}{2}$  the starting points are too bad. This avoids a fast convergency.

# **1.2.4** Fast OFDD based minimization of Fixed Polarity Reed-Muller Expressions **Prechsler** 1996]

this paper a Fast OFDD (Ordered Functional Decision Diagrams) based minimization for the proposed.

**Definition 2.2** A DD over  $X_n := \{x_1, x_2, ..., x_n\}$  is a rooted directed acyclic graph G = (V, E) with where x set V containing two types of vertices, non-terminal and terminal vertices. A non-terminal where x v is labeled with a variable from  $X_n$ , called the decision variable for v, and has exactly successors denoted by  $low(v), high(v) \in V$ . A terminal vertex v is labeled with a 0 or 1 and the successors.

**Definition 2.3** A DD is free if each variable is encountered at most once on each path in the DD the root to a terminal vertex. A DD is ordered if it is free and the variables are encountered the same order on each path in the DD from the root to a terminal vertex.

**The possible** to define certain reductions on the decision diagrams in order to reduce their size. **The reduction** types are used in this paper [Drechsler 1996]: Type I: Delete a node v' whose successors are identical to the successors of another node v and redirect the edges pointing to v' to point to v.

Type D: Delete all nodes v whose successor high(v) points to the terminal 0 and connect the incoming edges of the deleted node to the corresponding successor.

**Definition 2.4** A DD is reduced if no reductions can be applied to the DD. Two DDs, G1 and G2, are called *equivalent* iff G2 results from G1 by repeated applications of reductions and more reductions. A DD, G2, is called the *reduction* of a DD, G1, if G1 and G2 are equivalent and G2 itself is reduced.

**Definition 2.5** An OFDD over  $X_n$  is given by an ordered DD over  $X_n$  together with a uniquely intermined decomposition type (here, the positive Davio (1.3) and the negative Davio (1.4) expansions are termed as decomposition types),  $d_i \in \{pD, nD\}$  assigned to each variable  $x_i$

$z \in \{1, ..., n\}$ ). The function  $f_a : B^n \to B$  represented by an OFDD G over  $X_n$  is defined as:

- i. If G consists of a single node labeled with 0 (1), then G is an OFDD for f = 0 (f = 1).

- ii. If G has a root  $\nu$  with label  $x_i$ , then G is an OFDD for

$\begin{cases} f_{low(v)} \oplus x_i f_{high(v)} : d_i \text{ is } pD \\ f_{low(v)} \oplus \overline{x_i} f_{high(v)} : d_i \text{ is } nD \end{cases}$

where  $f_{low(v)}(f_{high(v)})$  is the function represented by the OFDD rooted at low(v)(high(v)).

**Definition 2.6** A node in an OFDD is called a positive Davio-node if it is expanded by Davio iccomposition (2.1) and it is called a negative Davio-node if it is expanded by Davio ecomposition (2.2).

Then the relation between OFDDs and FPRMs are outlined. This relation directly outlines methods for the construction of small or minimum FPRMs. In an OFDD a positive Davio or a megative Davio decomposition is carried out in each node. The reduction type D guarantees that a mode is deleted, if the function represented at this node is independent from the corresponding metable. The paths from the root of the OFDD to the terminal one (1) are closely observed. They are called 1-paths. Each 1-path defines a subset of the variables  $X_n$  that uniquely corresponds to a 1-term in the FPRM. Thus, the following theorem is derived.

**Theorem 2.6** The number of 1-paths in an OFDD for the Boolean function  $f : B^n \to B$  is and to the number of terms in the FPRM. The choice of decompositions in the OFDD actermines the polarity of the FPRM.

Solution is used, the variable in the FPRM is uncomplemented and it is complemented, if negative Davio decomposition is used. Obviously, the construction of the FRM from a given OFDD for a single output function has running time O(n|terms|), where *jerms* denotes the number of terms. The number of terms for the FPRM can easily be *intermined* from the OFDD for a single output function by a simple depth-first-search algorithm **text** counts the number of 1-paths. The algorithm has running time O(G). Thus, OFDDs with a *minimum* number of 1-paths to get FPRMs with a minimum number of terms is determined.

E an OFDD with fixed decompositions is given and the decomposition corresponding to one ratiable  $x_i$  is to be changed from positive Davio to negative Davio or vice versa this can be done efficiently in polynomial time as follows: An EXOR-operation is carried out at each node labeled with  $x_i$ .

To determine the minimum FPRM for a given function f an OFDD with only positive Daviomices is built up. Then it is transformed step by step to an OFDD with only negative Daviomices. OFDDs for each possible choice of decomposition types are constructed, *i.e.*  $2^n$  OFDDs reconstructed. For each OFDD the number of 1-paths is determined and the best result is microd.

The 2void the construction of the same OFDD two times, gray code is used to enumerate all **exempositions**. Although the algorithm is conceptually very simple, the experimental results that it performs very fast. One main reason for this, are the efficient operations on the **GFDDs**.

For all functions for which the OFDD can be constructed the minimum FPRM can be obtained. The can be done for (some) functions with several hundred variables. Thus, this approach is immed by the running time, but not by the space requirement.

# A semicustom IC for generating optimum generalized Reed-Muller expansions

[Almaini 1997] explains the theory and design of a semicustom integrated circuit (IC) the generation of the optimum polarity of a given Boolean function. Given the minterm set ents of a Boolean function, the chip computes coefficients of all the fixed polarities of the set end Reed-Muller (GRM) expansions, and identifies the polarity with the least number of

The X coefficients and GRM coefficients is based on the manual [Almaini 1996]. The X coefficients, where,  $X \in \{0,1\}$ , of the minterms are in a row and adjacent digits are EXORed to produce the below and so on. The resulting means elements of each row are the coefficients for  $f_0$ . It was observed that the right-most of each row are the coefficients for  $f_{15}$ . The transformation may be reversed if the formation of  $f_0$  and  $f_{15}$  are reversed.

the ASIC for a 4-variable function, with sixteen input lines, includes CONV, the manual converter, a four bit counter COUNT, ADD-which computes the weights of the sectors. Here, the weight refers to the number of logic ones, which is equal to the

sumber of terms. The weight is stored in REG while the coefficients of the polarity are stored in REGOUT. REG and REGOUT are 4 and 16 bit registers. These hold the weight of  $f_0$  and its coefficients and update their content only if a better polarity is found. COMP compares the seights of the present polarity and last best polarity. Polarity vectors are computed on the positive edge of clock pulse. By the end of the sixteenth clock pulse REGOUT hold the coefficients of the best polarity.

# **2.2.6** Mapping of fixed polarity Reed-Muller coefficients from minterms and the **minimization** of fixed polarity Reed-Muller expressions [Khan 1997]

in the paper [Khan 1997], an efficient and simple algorithm for mapping FPRM coefficients in the on-set minterms of the function for a given polarity vector is presented. Another instic algorithm for finding an optimal polarity vector from the on-set minterms that produces in near minimum FPRM expression is also presented. Both these algorithms are developed for insteaded functions.

For the purpose of mapping FPRM coefficients and the heuristic determination of an optimal vector from the on-set minterms, the following definitions and lemmas are required.

Emition 2.7 Let x be a variable and

$$e \in \{0, 1, 2\}$$

.  $x^e$  is a literal of x such that

$$\begin{bmatrix}

x & if e = 0 \\

e & if e = 1

\end{bmatrix}$$

$$x^{e} \begin{cases} x & if e = 0 \\ x & if e = 1 \\ 1 & if e = 2 \end{cases}$$

**The** *constant sum of products (CSOP)* for an arbitrary *n*-variable function f(X) is represented

$$\mathbf{1} = \sum_{k \in \{0, 1\}^n} a_k X^k = \sum_{k \in \{0, 1\}^n} a_k X^k$$

(2.3)

$\sum + and \sum \oplus$  represent OR-Sum and EXOR-Sum respectively,  $X = (x_1, x_2, ..., x_n)$  is  $\sum 2 = 2ble$  array,  $k = (k_1 \ k_2 \dots k_n) \in \{0, 1\}^n$  is the polarity *n*-tuple for the minterm  $= -i \in \{0, 1\}^n | a_k \in \{0, 1\}$  are the CSOP coefficients, and  $X^k = (x_1^{k_1} \ x_2^{k_2} \dots x_n^{k_n})$  is the corresponding to the coefficient  $a_k$  and exists iff  $a_k = 1$ .

**1.1 i. 1.8** Let  $y = (y_1 y_2 \dots y_n) \in \{0, 1, 2\}^n$ . The number of 1s in y is denoted by  $\tau(y)$ .

**2.9** The value of Boolean difference of an arbitrary function of *n*-variables f(X)**Example 1** to  $X^h$  at X = (0,0,...,0) is defined as

$$\frac{d^{\tau(h)}f(X)}{dX^{h}}\Big|_{(0,0,\dots,0)} = \sum_{m \in M} \oplus f(Z)$$

$$h = (h_1 h_2 \dots h_n) \in \{1, 2\}^n, \ dX^h = dx_1^{h_1} dx_2^{h_2} \dots dx_n^{h_n}, \ d^0 = d^1 = 1,$$

where  $M = \left\{ m = (m_1 m_2 \dots m_n) (\forall i) m_i = \begin{cases} 0, 1 \ if \ h_i = 1 \\ 2 \ if \ h_i = 2 \end{cases} \right\}, \ Z = (z_1 z_2 \dots z_n) \ and$

$(\forall i) z_i = \begin{cases} 0 \ if \ m_i = 0 \\ 1 \ if \ m_i = 1 \\ 2 \ if \ m_i = 2 \end{cases}$

**Definition 2.10**  $K_{on} = \left\{ k = (k_1 k_2 \dots k_n) \in \{0,1\}^n | a_k = 1 \right\}$  is the set of polarity *n*-tuples for the ONmeterms of f(X).  $K_{off} = \left\{ k = (k_1 k_2 \dots k_n) \in \{0,1\}^n | a_k = 0 \right\}$  is the set of polarity *n*-tuples for the ONmeterms of f(X).

**Theorem 2.7**  $b_{11...1} = 1$  if and only if  $|K_{on}|$  is odd.

**Theorem 2.8**  $(\forall t \in \{0, 1\}^n)b_l = \sum_{k \in K_{on}} \oplus d \text{ where } d^* = (d_1^*d_2^*...d_n^*) = (t \lor k \lor p) \land (t \lor \overline{k} \lor \overline{p}),$

$f = (p_1 p_2 \dots p_n) \in \{0, 1\}^n$  is the polarity vector for the variable array, and

$$d = \begin{cases} 1 & iff \quad (\forall i)d_i^* = 1 \\ 0 & iff \quad (\exists i)d_i^* = 0 \end{cases}$$

$\dots \wedge$  and  $\overline{}$  are bitwise operators.

**Theorem 2.9**  $b_{00...0} = 1$  iff  $p \in K_{on}$ .

Depending on Theorems 2.7-2.9, an algorithm is developed for mapping the FPRM coefficients  $\pm$ om the on-set minterms.

In this algorithm,  $|K_{on}|$  numbers of on-set minterms are to be stored, where average and maximum values of  $|K_{on}|$  are,

For 2<sup>n</sup>, respectively. Therefore, both the average and maximum space complexities of this **decrifthm** is  $O(2^n)$ , where the coefficient of the average complexity is 0.5 times that of the **average** and maximum computational time complexities of the **average** and maximum computational time complexities of the **average** and maximum complexity is 0.5 times that of the **average** complexity is 0.5 times that of the **average** are complexity.

**Definition 2.11** Let  $K_{on,i} = \left\{ k_i \mid k_i \text{ is the ith bit of } k \in \{0,1\}^n \text{ and } a_k = 1 \right\}$  be the set of *i*th bits of **meser** minterms.  $ONE(i) = \sum_{k \in K_{on}} k_i$  is the number of 1s in  $K_{on,i}$ .  $ZERO(i) = |K_{on}| - ONE(i)$  is the number of 0s in  $K_{on,i}$ .

tollowing observations were found during the experimentation of the algorithm.

**Conservation 2.1** If all product terms of the function are canonical product terms, i.e. minterms, the optimal value of  $p_i$  is likely to be 1 if  $|K_{on}|$  is even or both  $|K_{on}|$  and ONE(i) are odd; and the optimal value of  $p_i$  is likely to be 0 if  $|K_{on}|$  is odd and ONE(i) is even.

**Example 2.1** Let  $f(x_1, x_2, x_3) = \overline{x_1 x_2 x_3} + \overline{x_1 x_2 x_3} + \overline{x_1 x_2 x_3} + x_1 \overline{x_2 x_3}$ . Here, the function **example 3.1** Let  $f(x_1, x_2, x_3) = \overline{x_1 x_2 x_3} + \overline{x_1 x_2 x_3} + \overline{x_1 x_2 x_3} + x_1 \overline{x_2 x_3}$ . Here, the function **example 3.1** Let  $f(x_1, x_2, x_3) = \overline{x_1 x_2 x_3} + \overline{x_1 x_2 x_3} + \overline{x_1 x_2 x_3} + x_1 \overline{x_2 x_3}$ . Here, the function **example 3.1** Let  $f(x_1, x_2, x_3) = \overline{x_1 x_2 x_3} + \overline{x_1 x_2 x_3} + \overline{x_1 x_2 x_3} + x_1 \overline{x_2 x_3}$ .

**Observation 2.2** If some product terms of the function are non-canonical product terms, then optimal value of  $p_i$  is likely to be 1 if  $ONE(i) \ge ZERO(i)$ ; and the optimal value of  $p_i$  is likely to be 0 if ONE(i) < ZERO(i).

**Example 2.2** Let  $f(x_1, x_2, x_3) = \overline{x_1 x_2 x_3} + \overline{x_1 x_3} + x_1 x_3$ . Here, ONE(1) = 1, ZERO(1) = 2, ONE(3) = 2, and ZERO(3) = 1. Therefore, the optimal value of  $p_1$  is likely to be 0 and the extimal value of  $p_3$  is likely to be 1.

**Lemma 2.1** If a function  $f(x_1, x_2, ..., x_n)$  contains only minterms and  $ONE(i) = |K_{on}|$ , then  $\Rightarrow x_i f_2$  (expansion using  $p_i = 1$ ) contains the same set of minterms as the original function. Similarly, if a function  $f(x_1, x_2, ..., x_n)$  contains only minterms and ONE(i) = 0, then  $f_{\bullet} \oplus \overline{x_i} f_2$ respansion using  $p_i = 0$ ) contains the same set of minterms as the original function. **Example** on Observations 2.1 and 2.2 and Lemma 2.1, an algorithm is developed for **Example** finding an optimal polarity vector from on-set minterms that produces the near **Example** FPRM expressions. The maximum and the average computational time of this algorithm  $(2^{\mu}n2^{n})$ .

# **Sympathy: Fast Exact Minimization of Fixed Polarity Reed-Muller Expressions for Symmetric Functions** [Drechsler 1997]

an exact algorithm, *Sympathy* has been implemented, to minimize FPRMs for symmetric **symmetric** and the required computation time is polynomial. In [Drechsler 1996] close relations **seen** OFDDs and FPRMs have been investigated.

The definition of OFDD and related terms are described in the previous section.

**Theorem 2.10** Let  $G_1$ ,  $G_2$  be OFDDs with the same Decomposition Type List (DTL) d and with the same ordering. Then the EXOR-synthesis of  $G_1$  and  $G_2$  can be performed by an algorithm of memplexity  $O(|G_1| \cdot |G_2|)$  resulting in an OFDD bounded by the same size.

Symmetric functions are used here. Let  $f : B^n \to B$  be a totally defined Boolean function and  $\mathbb{X}_* := \{x_1, x_2, ..., x_n\}$  be the corresponding set of variables. The function f is said to be symmetric  $\mathbb{Y}_*$  respect to a set  $S \subseteq X_n$  if f remains invariant under all permutations of the variables in S. For respect to a set  $S \subseteq X_n$  if f remains the symmetry is an equivalence relation which partitions the  $\mathbb{Y}_*$  into disjoint classes  $S_1, ..., S_k$  that will be named the symmetry sets. A function f is called  $\mathbb{Y}_*$  into disjoint classes  $S_1, ..., S_k$  that will be named the symmetry sets. A function f is called  $\mathbb{Y}_*$  introduces if it has at least one symmetry set  $S_i$  with  $S_i > 1$ . If a function f has only one  $\mathbb{Y}_*$  immetric function. If  $x_i, x_j \in S_l \subseteq X_n \ x_i \neq x_j$  and  $1 \le l \le k$  f is called *pairwise symmetric* in  $\mathbb{Y}_*$ . A simple consequence of pairwise symmetry is the following lemma.

**Lemma 2.2** A function is pairwise symmetric in  $(x_i, x_j)$  iff  $f_{x_i x_j} = f_{\overline{x_i x_j}}$

in the following paragraphs the problem of finding minimal FPRMs for totally symmetric functions is considered. The results will also be applied to partially symmetric functions.

a is showed below that the number of different FPRMs that have to be considered during minimization of FPRMs for symmetric functions can be tremendously reduced.

**Theorem 2.11** Let f be pair-wise symmetric in  $(x_i, x_j)$ . For Decomposition Type Lists (DTLs)  $\vec{x} = (d_1 \dots d_i \dots d_j \dots d_n)$  and  $d' = (d_1 \dots d_i \dots d_j \dots d_n)$  it holds  $|f_d| = |f_{d'}|$ . Lemma 2.2 a straightforward computation shows that it does not influence the number of whether f is first decomposed by pD for  $x_i$  and then by nD for  $x_j$  or first by nD for  $x_i$ . It then by pD for  $x_j$ . From the theorem it is obtained:

**Evaluary 2.1** There exist at most n+1 FPRMs for a totally symmetric function that differ in size. The Corollary found that it is sufficient in the following to only consider FPRMs for the set m = n + 1 DTLs:  $D = \begin{cases} d^i \mid d^i = (nd)^i (pd)^{n-i} \land 0 \le i \le n \end{cases}$ .

**EVALUATE:** OFDDs are used for the construction of the FPRMs and a polynomial algorithm is aimed r = minimization, it is to be proved that an OFDD for a totally symmetric function has at polynomial size in the number of *n* variables.

the following, given is an upper bound for the size of the OFDDs for totally symmetric terms with DTLs as they will occur in the exact algorithm.

**Theorem 2.12** Each OFDD with DTL  $d^i \in D(i \in \{0,...,n\})$  that represents a totally symmetric function f has size  $O(n^3)$ .

Less the size of OFDDs with only positive Davio-nodes is  $O(n^2)$ . (The same argumentation for OFDDs with only negative Davio-nodes.) Then the case where the upper variables are posed by negative Davio-nodes are considered, while the lower variables are decomposed restrice Davio-nodes. The assertion of the theorem then follows from the fact that the lowest feedback by negative Davio-nodes has at most *n* nodes and that the functions  $f_{x_k}$  and  $f_{x_k} = f_{x_k}$  of a totally symmetric function *f* are totally symmetric.

**Descrem 2.13** The transformation of an OFDD with DTL  $d^i \in D(i \in \{0, ..., n-1\})$  of a totally **example** function f of n variables to an OFDD with DTL  $d^{i+1} \in D$  has time and space exity  $O(n^6)$ .

**Descen 2.14** The exact algorithm for the FPRM minimization of a totally symmetric function f $f = \pm ables$  has running time  $O(n^7)$  and space requirement  $O(n^6)$ .

The running time of the algorithm is dominated by the transformation (from Theorem Thus, the overall performance of the algorithm is directly obtained, since the maximum has to be carried out *n* times. The space requirement is  $O(n^6)$ , since this is the maximum the transformation. (The resulting OFDDs have at most size  $O(n^3)$ .)

behavior of the EXOR-operation) all experiments have shown that the algorithm is very fast shows linear behavior with respect to the running time.

# Exact minimization of Fixed Polarity Reed-Muller expressions for **5** mpletely Specified Functions [Debnath 2000]

paper [Debnath 2000], the operators '+' and '-' indicate arithmetic and mod-2 addition, ectively.

**Example 1** function f is a mapping  $f : \{0,1\}^n \to \{0,1\}$  and an *n*-table integer valued function g is a mapping  $g : \{0,1\}^n \to \{0,1,...,p-1\}$  where p < 2.

**Example 1.13** An *n*-variable integer-valued function  $f(x_1, x_2, ..., x_n)$  can be written as  $m_j x_1^{b_1} x_2^{b_2} ... x_n^{b_n}$  where  $m_j \in \{0, 1, ..., p-1\}$   $(p \ge 2), b_1, b_2, ..., b_n \in \{0, 1\}$  such that  $b_1 b_2 ... b_n$  is *n*-bit binary number representing j,  $x_i^{b_i} = \overline{x_i}$  when  $b_i = 0, x_i^{b_i} = x_i$  when = 1, and i = 1, 2, ..., n. Then  $[m_0, m_1, ..., m_{2^n-1}]$  is the truth vector of f.

**Example 2.3** The truth vector of the three-variable switching function  $\overline{x_1 x_2 x_3} \lor x_1$  is  $x_1, 0, 1, 1, 1, 1$ , and that of the three-variable integer-valued function  $3x_1 + 4x_2x_3 + 2x_3$  is 2, 4, 5, 3, 5, 7].

In *n*-variable completely specified switching function there are  $2^n$  distinct FPRMs, and the minimum problem is to find a polarity vector that produces an FPRM with minimum number bodies. On the other hand, for an *n*-variable incompletely specified switching function with especified minterms there are  $2^{n+\alpha}$  distinct FPRMs, and the minimization problem is to find a carity vector and an assignment of the unspecified minterms to 0's and 1's that produce an M with minimum number of products. Once the polarity vector and the assignment of the unspecified minterms are determined, generation of an FPRM is relatively easy [Davio 1978, 1996].

the thod for the exact minimization of FPRMs for three-variable switching function has been based in this paper. The method is based on the computation of *extended truth vector* and the vector [Davio 1978, Sasao 1996]. In general, for an *n*-variable completely specified the bing function, extended truth vector is a binary vector  $[t_0, t_1, ..., t_{3^n-1}]$  with  $3^n$  elements, and the vector is an integer vector  $[w_0, w_1, ..., w_{2^n-1}]$  with  $[t_0, t_1, ..., t_{3^n-1}]$  elements. Each element the weight vector is associated with a *polarity vector*. For an *n*-variable switching function f, polarity vector for  $w_j$  is a binary vector  $(b_1, b_2, ..., b_n)$ with that  $b_1, b_2, ..., b_n$  the *n*-bit binary number representing j,  $(j = 0, 1, ..., 2^n - 1)$ , and  $w_j$ metresents the number of products in the FPRM for f with polarity vector  $(b_1, b_2, ..., b_n)$ .

For an *n*-variable switching function with  $\alpha$  unspecified minterms  $d_1, d_2, ..., d_{\alpha}$ , extended truth vector is a vector of switching functions  $t_i(d_1, d_2, ..., d_{\alpha})(i = 0, 1, ..., 3^n - 1)$ , and weight vector is a vector of integer-valued functions  $w_j(d_1, d_2, ..., d_{\alpha})(j = 0, 1, ..., 2^n - 1)$ .

**Definition 2.14** Let the *minimum value* of the  $\alpha$ -variable integer-valued function  $*d_1, d_2, ..., d_{\alpha}$ , denoted by  $w^{\min}$ , be  $\min_{0 \le i \le 2^n - 1} m_i$ , where  $[m_0, m_1, ..., m_{2^{\alpha} - 1}]$  represents the **multiple vector** for w.

Let  $[w_0, w_1, ..., w_{2^n-1}]$  be the weight vector for an *n*-variable incompletely specified switching inction  $f(x_1, x_2, ..., x_n)$ , and  $w_j^{\min}$  be the minimum value for  $w_j(d_1, d_2, ..., d_{\alpha})$  where  $d_{-1}d_{2}, ..., d_{\alpha}$  represent unspecified minterms of f. Let  $0 \le k \le 2^n - 1$  and  $a_1, a_2, ..., a_{\alpha} \in \{0, 1\}$ where  $w_k(a_1, a_2, ..., a_{\alpha}) = \min_{0 \le i \le 2^n - 1} w_j^{\min}$ . Let  $c_1, c_2, ..., c_n$  be the *n*-bit binary number metersenting k. Then,  $(a_1, a_2, ..., a_{\alpha})$  represents an assignment of  $(d_1, d_2, ..., d_{\alpha})$  and  $(c_1, c_2, ..., c_n)$ metersents a polarity vector that produces a minimum FPRM for f.

T: manipulate integer-valued function a multi-terminal binary decision diagram (MTBDD) [Carke 1993] is used. An MTBDD, which is a natural extension of binary decision diagram (EDD) [Bryant 1986], is a directed acyclic graph with multiple terminal nodes each of which has a categor value.

Fraightforward method to build MTBDDs for weight vector requires excessive computation and memory resources, because they represent all possible FPRMs for the given mempletely specified function. However, the concentration is in an FPRM with the fewest inducts. Suppose there is an FPRM for the given function with  $t_{threshold+1}$  products, then it is ficient to search for an FPRM with  $t_{threshold}$  or fewer products. If such an FPRM does not then the FPRM with  $t_{threshold+1}$  products is the minimum FPRM. Thus, to restrict the search without sacrificing the minimality of the solution, we use *threshold value*,  $t_{threshold}$ , during function of MTBDDs. The threshold value can be obtained by using any simplification for FPRMs.

**Exact** on the above discussions, an algorithm for exact minimization of FPRM for incompletely f is developed.

implementation of the developed algorithm it is revealed that the factors on which the mainly depends are the threshold value, the number of variables in the faction, and the number of unspecified minterms. The implementation results shown in this

with any number of unspecified minterms. However, for functions with nine or more mables it often requires excessive CPU time and memory resources when the number of memory resources when the number of memory is more than 30.

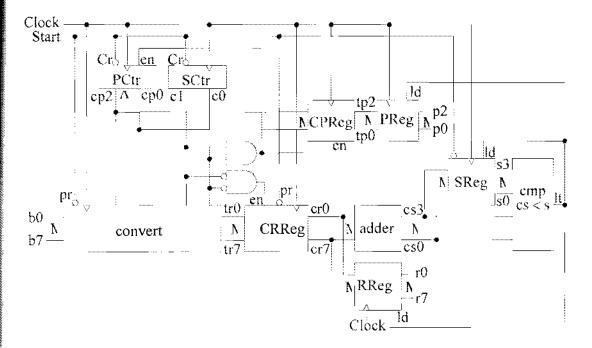

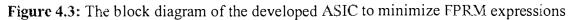

# apter 3 production to Application Specific Integrated Circuits (ASICs)

#### Introduction

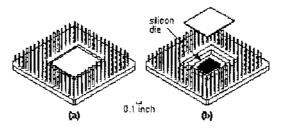

ASIC is an *application-specific integrated circuit*. Before knowing what an ASIC is let us bok at the evolution of the silicon chip or integrated circuit (IC). [Smith 1997]

will go through holes in a printed-circuit board). People often call the package a chip, but the solution of t

Figure 3.1: An integrated circuit (IC). (a) A pin-grid array (PGA) package. (b) The silicon die or chip is under the package lid.

Examples of ICs that are not ASICs include standard parts such as: memory chips sold as a memory item—read only memory (ROMs), dynamic random-access memory (DRAM), and are RAM (SRAM); microprocessors; transistor-transistor logic (TTL) or TTL-equivalent ICs at all-scale integration (SSI), medium-scale integration (MSI), and large-scale integration (LSI) evels.

Examples of ICs that *are* ASICs include: a chip for a toy bear that talks; a chip for a satellite; a top designed to handle the interface between memory and a microprocessor for a workstation **CPU**; and a chip containing a microprocessor as a cell together with other logic. Two ICs that eight or might not be considered ASICs are a controller chip for a PC and a chip for a modem. So the of these examples are specific to an application (shades of an ASIC) but are sold to many efferent system vendors (shades of a standard part). ASICs such as these are sometimes called *eplication-specific standard products (ASSPs)*.

# Types of ASICs

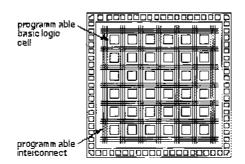

Is are made on a thin (a few hundred microns (a micron is  $10^{-6}$  m) thick), circular silicon *icir*, with each wafer holding hundreds of die (sometimes people use dies or dice for the plural *icie*). The transistors and wiring are made from many layers (usually between 10 and 15 **icinct** layers) built on top of one another. Each successive *mask layer* has a pattern that is fined using a *mask* similar to a glass photographic slide. The first half-dozen or so layers the transistors. The last half-dozen or so layers define the metal wires between the misistors (the *interconnect*).

time different types of ASICs discussed below are,

- Full Custom ASICs

- = Semicustom ASICs

- Programmable ASICs

# 3.2.1 Full Custom ASICs

**I** i full-custom ASIC an engineer designs some or all of the logic cells, circuits, or layout recifically for one ASIC. This means the designer abandons the approach of using pretested and recharacterized cells for all or part of that design. It makes sense to take this approach only if form are no suitable existing cell libraries available that can be used for the entire design. This might be because existing cell libraries are not fast enough, or the logic cells are not small or ight or consume too much power. A full-custom design may be needed if the ASIC rechnology is new or so specialized that there are no existing cell libraries or because the ASIC is specialized that some circuits must be custom designed.

# 3.2.2 Semicustom ASICs

Semicustom ASICs are,

- Standard Cell based ASICs

- ☆ Gate Array based ASICs

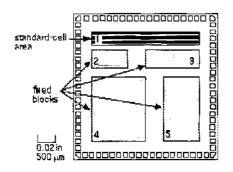

# **3.2.2.1** Standard-Cell–Based ASICs

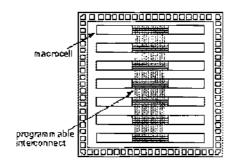

▲ *cell-based ASIC (cell-based IC, or CBIC)* uses predesigned logic cells (AND gates, OR gates, include the cells and flip-flops, for example) known as *standard cells*. It is generally accepted that a accepted ASIC or CBIC means a standard-cell-based ASIC.

The standard-cell areas (also called flexible blocks) in a CBIC are built of rows of standard cells—like a wall built of bricks. The standard-cell areas may be used in combination with larger precisigned cells, perhaps microcontrollers or even microprocessors, known as *megacells*.

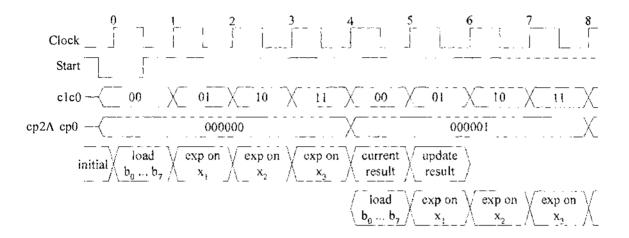

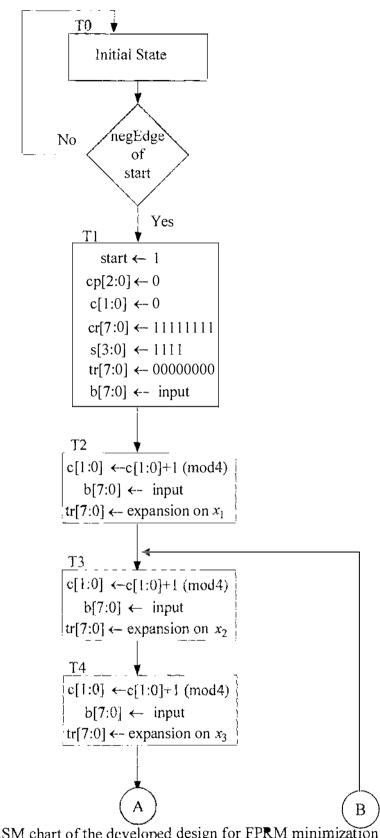

degacells are also called megafunctions, full-custom blocks, system-level macros (SLMs), fixed kocks, cores, or Functional Standard Blocks (FSBs).