**Department of EEE**

## **Process simulation of FILOX vertical MOSFET to estimate**

## fabrication parameters.

By

**Tarikul Islam Milon**

(ID: 2011-3-80-014)

And

#### **Kousar Hossain**

(ID: 2011-3-80-022)

And

Fara Jannat Shova

(ID: 2011-3-80-023)

Submitted to the

Department of Electrical & Electronics Engineering, Faculty of Science and Engineering, East West University

In partial fulfillment of the requirements for the degree of Bachelor of Science

in Electrical & Electronics Engineering (B.Sc. in EEE)

Fall, 2015

Approved By

Thesis Advisor

Dr. Mohammad Mojammel AL Hakim

Department Chairperson Dr. Muhammed Mazharul Islam

## Approval

The thesis title "Process simulation of FILOX vertical MOSFET to estimate fabrication parameters" submitted by Tarikul Islam Milon [2011-3-80-014], Kousar Hossain [2011-3-80-022] and Fara Jannat Shova [2011-3-80-023] in the semester of fall-2015 is approved satisfactory in partial fulfillment of the requirements for the requirements for the degree of Bachelor of Science in Electrical and Electronics Engineering.

Dr. Mohammad Mojammel AL Hakim

Associate Professor, Department of Electrical and Electronics Engineering

East West University, Dhaka, Bangladesh

## Declaration

We, hereby declare that this material which we now submit for assessment on the program of study leading to the award of Bachelor's Degree in Electrical and Electronics Engineering is entirely our own work and we have exercised reasonable care to ensure that the work is original and does not to the best of our knowledge breach any law of copyright, and has not been taken from the work of others. Any reference from outside source has been cited and acknowledged within the text of our work.

Tarikul Islam Milon

Kousar Hossain

Fara Jannat Shova

Fall Semester

December' 2015

## ABSTRACT

The aim of this thesis work is to study the Process simulation of FILOX vertical MOSFET to estimate fabrication parameters for RF application. Double gate or surround-gate vertical metal oxide semiconductor field effect transistors is delayed by the parasitic overlap capacitance related with their layout, which is larger than for a lateral MOSFET on the same technology node. A simple self-aligned process has been developed to reduce the parasitic overlap capacitance in vertical MOSFETs using nitride spacers on the sidewalls of the trench or pillar and a local oxidation. In this thesis we describe different steps of FILOX vertical MOSFET fabrication and finally we get 115nm of channel length, 140nm of junction depth, 3.3nm of gate oxide thickness,  $4 \times 10^{18}$  cm<sup>-3</sup> of body doping and  $2 \times 10^{20}$  cm<sup>-3</sup> of source/drain doping in the FILOX vertical MOSFET. We also describe the parameters that required to be changed to obtain different desired body doping value for our FILOX vertical MOSFET. This thesis we observed that decrease in dose of p-type implantation causes a decrease in body doping but this also changes the channel length. Therefore, to obtain our targeted channel length 115nm and junction depth 140nm we have to decrease the energy too. Simultaneously, we slightly need to decrease the dose and energy of n-type implantation. To get the desired body doping we see the alteration of channel length 115nm and junction depth 140nm. Then we adjusted the dose and energy of FILOX vertical MOSFET.

## ACKNOWLEDGEMENTS

First and foremost, we thank Allah for everything that has made this dissertation possible. We would like to sincerely thank our supervisor, Dr. Mohammad Mojammel Al Hakim for his patient guidance throughout our work. He has always been very encouraging, and offered invaluable advice as to which paths to pursue our work. His profound knowledge about our thesis topic has displayed an effective way to achieve our goal smoothly. Hence, we owe our deepest gratitude to our supervisor to give us some time during this thesis from his valuable time.

Thank and acknowledge also go to our Chairperson & Associate Professor, Department of Electrical and Electronic Engineering, especially Dr. Muhammed Mazharul Islam for his constant guidance, supervision, constructive suggestions.

We wish to express our deepest gratitude to Md. Delowar Hossain and Md. Jakaria Yusuf Khan for helping us to solve some sophisticated theoretical problems during our thesis. Their helpful hand and friendly behavior made us happy and the thesis easy.

We are much obliged to our family for their support and love shown over the years for supporting us and helping us get through the difficult times.

# AUTHORIZATION

We hereby declare that we are the sole author of this thesis and it has not been submitted elsewhere for the award of any degree or diploma. We authorize East West University to lend this thesis to other institutions or individual on request for the purpose of scholarly research only. We further authorize East West University to reproduce this thesis by photocopy or other means in total or in part at the request of other institutions or individuals for the purpose of scholarly research only after one year of submission.

Tarikul Islam Milon

Kousar Hossain

Fara Jannat Shova

## **Table of Content**

| APPROVAL<br>DECLARATION                                  |        |

|----------------------------------------------------------|--------|

| ACKNOWLEDGEMENTS                                         |        |

| ABSTRACT                                                 |        |

| AUTHORIZATION                                            |        |

| LIST OF FIGURE                                           | 8      |

| 1 CHAPTER: INRODUCTION                                   |        |

| 1.1 Motivation                                           | 10     |

| 1.2 Vertical MOSFETs and its Background                  | 10     |

| 1.2.1 Vertical MOSFETs based on epitaxy                  | 11     |

| 1.2.2 Vertical replacement gate MOSFETs                  | 12     |

| 1.2.3 Vertical MOSFETs based on ion implantation         | 13     |

| 1.3 Thesis Objective:                                    | 14     |

| 1.4 Organization:                                        | 14     |

| 2 CHAPTER: SIMULATION METHODOLOGY                        | 15     |

| 2.1 Simulation Overview                                  | 15     |

| 2.2 Simulation profile                                   | 16     |

| 2.2.1 The compress model                                 | 16     |

| 2.2.2 The viscous model                                  | 17     |

| 2.2.3 The Fermi Model                                    | 19     |

| <b>3 CHAPTER: RESULT</b>                                 | 21     |

| 3.1 FILOX vertical MOSFET Fabrication Process            | 21     |

| 3.2 Process parameter for desired different Body and S/D | doping |

| values                                                   |        |

| 4 CHAPTER                                                |        |

| 4.1 CONCLUSION                                           | 32     |

| 4.2 Table                                                | 32     |

| REFERENCES                                               |        |

# List of figure

| Figure 1-1:Vertical MOSFET based on epitaxy                                                                                           | .11 |

|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 1-2: Vertical MOSFET based on selective epitaxy with reduced overlap capacitanc                                                | 12  |

| Figure 1-3:Vertical replacement gate MOSFET                                                                                           | 13  |

| Figure 1-4: Vertical MOSFET based on ion implantation                                                                                 | 13  |

| Figure 2-1: Schematic structure of FILOX vertical MOSFET.                                                                             | 15  |

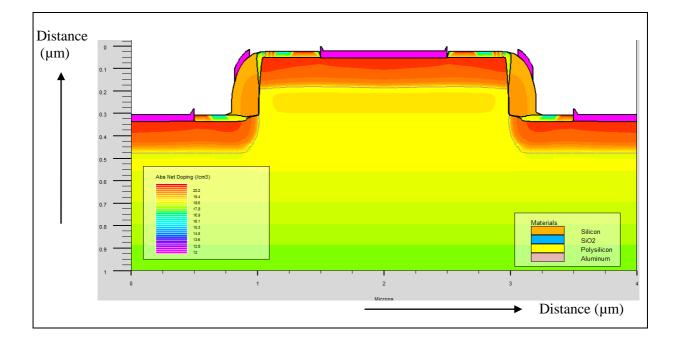

| Figure 2-2: Cross-sectional view of FILOX vertical MOSFET for showing the grid density                                                | 16  |

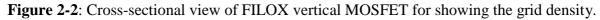

| <b>Figure 3-1</b> : Net doping $5.0 \times 10^{14}$ cm <sup>-3</sup> of silicon wafer of FILOX vertical MOSFET.                       | 21  |

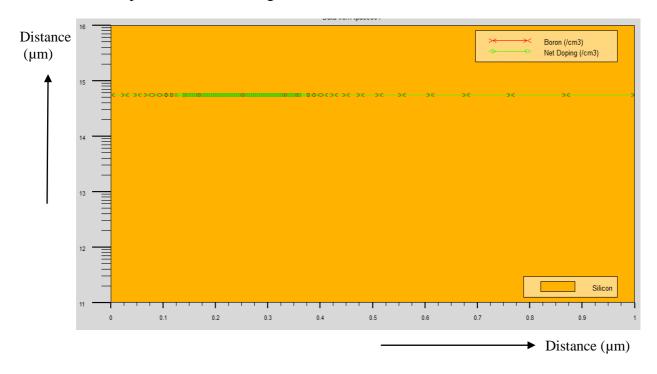

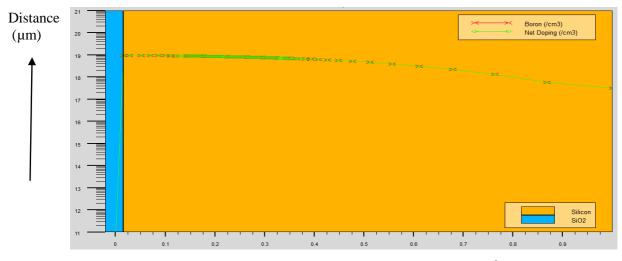

| Figure 3-2: Net doping $1.0 \times 10^{18}$ cm <sup>-3</sup> by implanted with boron dose= $5 \times 10^{14}$ cm <sup>-2</sup> of and |     |

| energy=50 kev of silicon wafer of FILOX vertical MOSFET                                                                               | 22  |

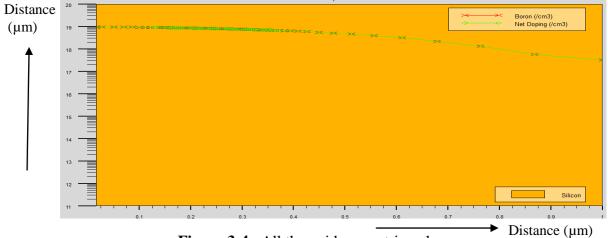

| <b>Figure 3-3</b> : Net doping $1.0 \times 10^{19}$ cm <sup>-3</sup> after drive in                                                   | 22  |

| Figure 3-4: All the oxides are stripped                                                                                               | 22  |

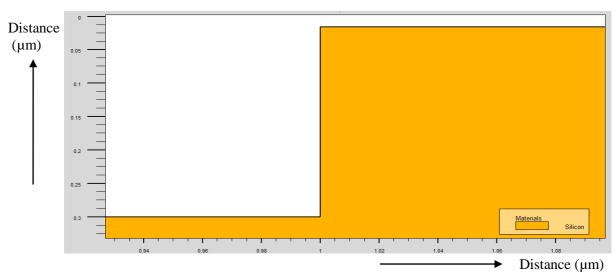

| Figure 3-5: 300nm pillar formation using dry etch                                                                                     | 23  |

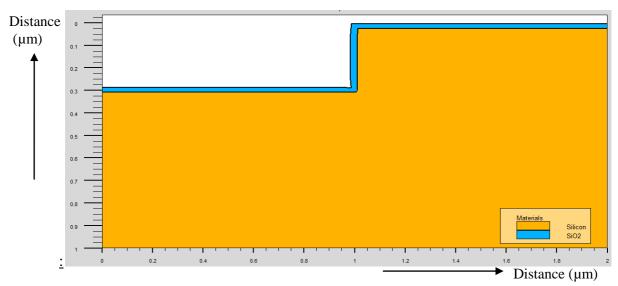

| Figure 3-6: Deposition of pad oxide oxide=10 nm on the Pillar.                                                                        | 23  |

| Figure 3-7: Deposition of Nitride Spacer =70nm on pad oxide                                                                           | 23  |

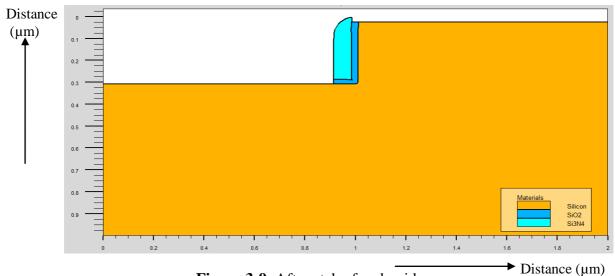

| Figure 3-8: After dry etching of nitride spacer.                                                                                      | 24  |

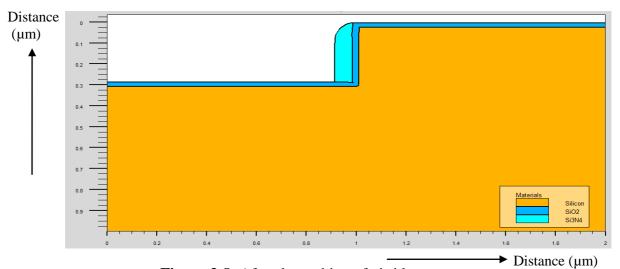

| Figure 3-9: After etch of pad oxide                                                                                                   | 24  |

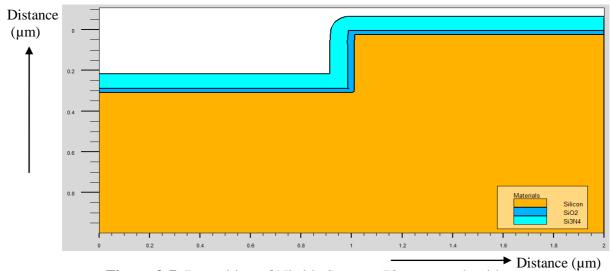

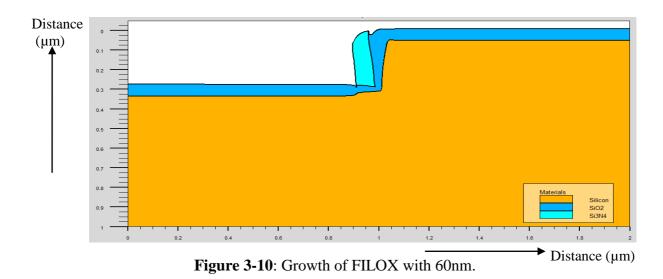

| Figure 3-10: Growth of FILOX with 60nm.                                                                                               | 24  |

| <b>Figure3-11</b> : Implantation of Arsenic dose= $6 \times 10^{15}$ cm <sup>-2</sup> and energy=90 kev of n-type source              |     |

| and drain                                                                                                                             | 25  |

| Figure 3-12: Removal of nitride fillet                                                                                                | 25  |

| Figure 3-13: Wet etch of oxide from sidewalls of pillar                                                                               | 25  |

| Figure 3-14: Deposition of gate oxide of thickness 3.3nm.                                                                             |     |

| Figure 3-15: Deposition of polysilicon of 200nm thickness                                                                             | 26  |

| Figure 3-16: Formation of polysilicon gate by dry etch.                                                                               | 26  |

| Figure 3-17: After rapid thermal Annealing using Fermi compress.                                                                      |     |

| Figure 3-18: Pattern of source and drain for metal contact of FILOX vertical MOSFET                                                   | 27  |

| Figure 3-19: Aluminum deposition and etching to create S/D, gate contact formation of                                                 |     |

| FILOX vertical MOSFET.                                                                                                                | 27  |

| Figure 3-20: Right mirror and Complete structure of FILOX vertical MOSFET.                                                            |     |

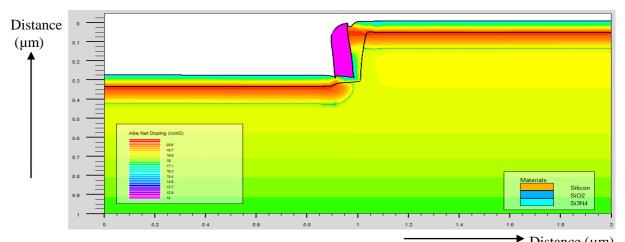

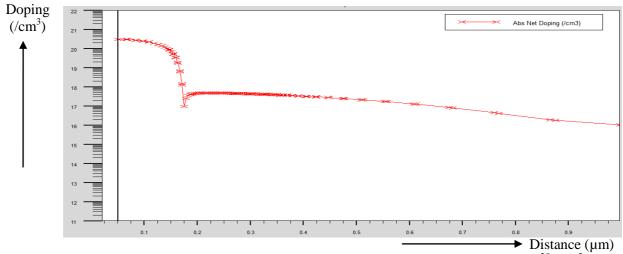

| <b>Figure 3-21</b> :115 channel length FILOX vertical MOSFET with S/D doping $2 \times 10^{20}$ cm <sup>-3</sup> and                  |     |

| net body doping of $4 \times 10^{18}$ cm <sup>-3</sup>                                                                                | 28  |

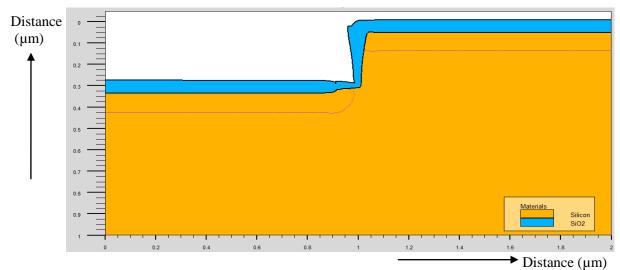

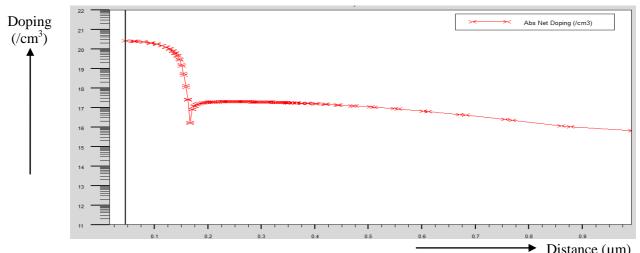

| <b>Figure 3-22</b> : 115 channel length FILOX vertical MOSFET with S/D doping $2 \times 10^{20}$ cm <sup>-3</sup> and |    |

|-----------------------------------------------------------------------------------------------------------------------|----|

| net body doping of $2 \times 10^{18}$ cm <sup>-3</sup> .                                                              | 29 |

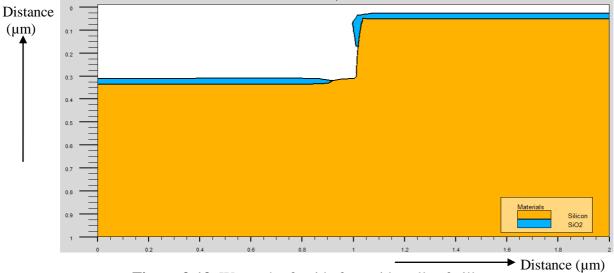

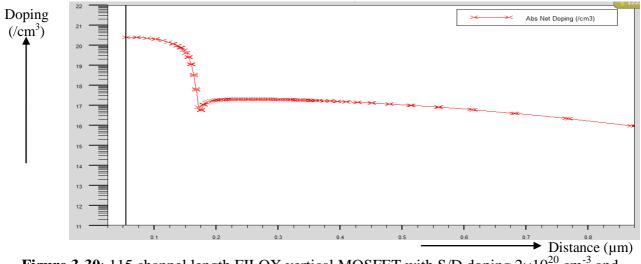

| <b>Figure 3-23</b> :115 channel length FILOX vertical MOSFET with S/D doping $2 \times 10^{20}$ cm <sup>-3</sup> and  |    |

| net body doping of $1 \times 10^{18}$ cm <sup>-3</sup>                                                                | 29 |

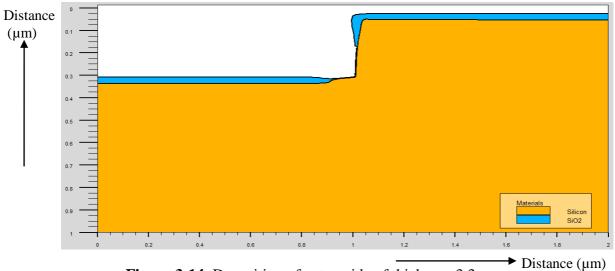

| <b>Figure 3-24</b> : 115 channel length FILOX vertical MOSFET with S/D doping $2 \times 10^{20}$ cm <sup>-3</sup> and |    |

| net body doping of $8 \times 10^{17}$ cm <sup>-3</sup>                                                                | 29 |

| <b>Figure 3-25</b> : 115 channel length FILOX vertical MOSFET with S/D doping $2 \times 10^{20}$ cm <sup>-3</sup> and |    |

| net body doping of $6 \times 10^{17}$ cm <sup>-3</sup> .                                                              | 30 |

| <b>Figure 3-26</b> :115 channel length FILOX vertical MOSFET with S/D doping $2 \times 10^{20}$ cm <sup>-3</sup> and  |    |

| net body doping of $4 \times 10^{17}$ cm <sup>-3</sup>                                                                | 30 |

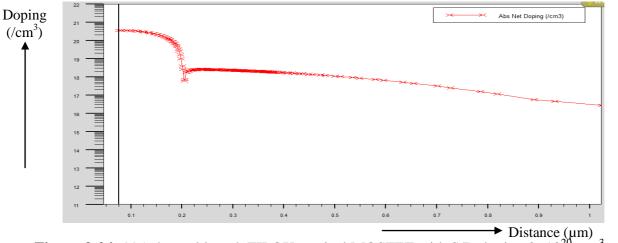

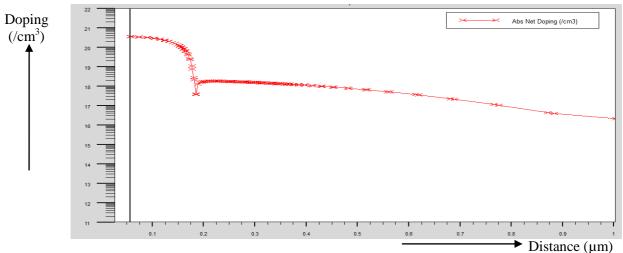

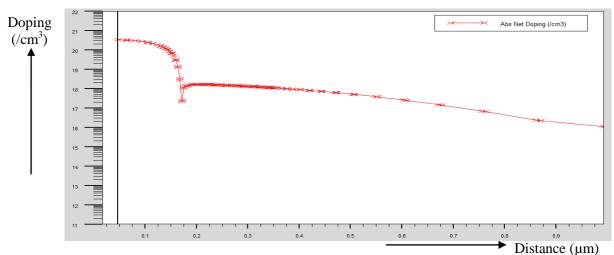

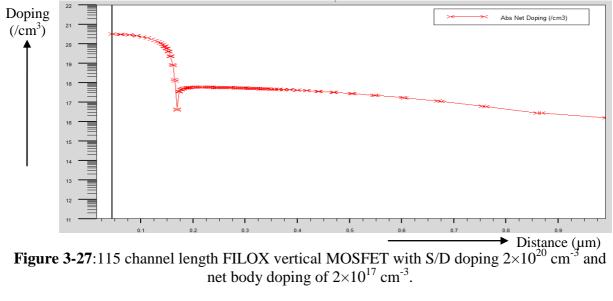

| <b>Figure 3-27</b> :115 channel length FILOX vertical MOSFET with S/D doping $2 \times 10^{20}$ cm <sup>-3</sup> and  |    |

| net body doping of $2 \times 10^{17}$ cm <sup>-3</sup>                                                                | 30 |

| Figure 3-28:115 channel length FILOX vertical MOSFET with S/D doping $2 \times 10^{20}$ cm <sup>-3</sup> and          |    |

| net body doping of $1 \times 10^{17}$ cm <sup>-3</sup>                                                                | 31 |

| <b>Figure 3-29</b> : 115 channel length FILOX vertical MOSFET with S/D doping $2 \times 10^{20}$ cm <sup>-3</sup> and |    |

| net body doping of $8 \times 10^{16}$ cm <sup>-3</sup>                                                                | 31 |

| <b>Figure 3-30</b> : 115 channel length FILOX vertical MOSFET with S/D doping $2 \times 10^{20}$ cm <sup>-3</sup> and |    |

| net body doping of $6 \times 10^{16}$ cm <sup>-3</sup>                                                                | 31 |

### **1 CHAPTER: INRODUCTION**

#### 1.1 Motivation

In modern CMOS technology the MOSFETs has been scaled down in size. Small MOSFETs are desirable for several reasons. The main reason of making transistors small is to pack more devices in a smaller chip area. This results in a chip with more functionality in same area. It is expected that smaller transistors will provide faster operation. Scaling of the MOSFETs require all devices dimension to be reduced proportionally.

The device dimensions are channel length, Junction depth and gate oxide thickness. Due to scale down of the MOSFETs size when the channel length of MOSFETs is 115nm some operational problems occur which is known as short channel effect (SCE) including hot carrier effects, punch-through effect, velocity saturation effect etc. Moreover, the fabrication cost of conventional planar MOSFETs below 115nm channel lengths is extremely expensive due to expensive lithography requirement to define the channel region.

Many types of alternative architectures are investigated to eliminate the short channel effect and to reduce the MOS fabrication cost in conventional silicon based technology. Such as,

- FINFET.

- Planner double gate MOSFETs.

- and Vertical MOSFETs etc.

#### 1.2 Vertical MOSFETs and its Background

Among these different device structures investigated vertical MOSFETs are potentially attractive due to following reasons.

- 1. Easier realization of surround gate structures.

- 2. Flexibility of designing short channel devices using relaxed lithography node.

- 3. Decoupling of the gate length from the packing density.

- 4. Less silicon area requirement to fabricate a vertical MOSFET

There have been several approaches investigated for designing and fabrication of vertical MOSFETs. These approaches are separated as three different types of vertical MOSFETs such as,

Type 1 - Vertical MOSFETs based on epitaxy.

Type 2 - Vertical replacement gate MOSFETs.

Type 3 - Vertical MOSFETs based on ion implantation.

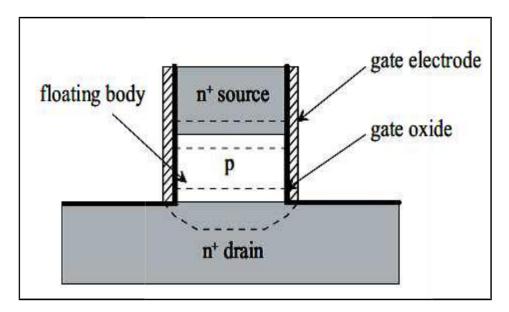

#### 1.2.1 Vertical MOSFETs based on epitaxy

A MOSFETs transistor of type 1, vertical MOSFETs based on epitaxy [1-5] is manufactured by accurately growing epitaxial layers for the heavily doped (n+) drain and source and p type channel illustrated in figure 1-1 For good control of channel length accurate epitaxy is needed. That can be achieved by using controlled low pressure chemical vapor deposition (LPCVD), to grow single crystal material on substrate. After epitaxy process a vertical MOSFETs transistor is manufactured by a pillar etch, gate oxide growth and finally a polysilicon gate is deposited and patterned. The main disadvantage of this technique is the integration of epitaxial layer into a standard CMOS process. Both source and drain extend across the full width of the pillar, this configuration gives very high parasitic bipolar transistor action. Another major disadvantage is the source/ drain overlap capacitance as polisilicon gate passes over the pillar top and bottom respectively for lithographic alignment tolerance and gate track to contact.

Figure 1-1: Vertical MOSFET based on epitaxy.

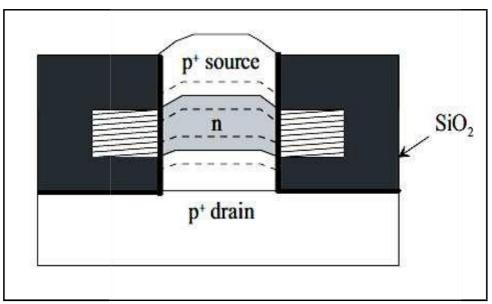

A variant of epitaxy approach has also been developed, which uses selective epitaxy [6-10] as illustrated in figure 1-2. In this approach, an oxide/ polysilicon/ oxide stock is created before the epitaxy. Then a trench is created by dry etches and gate oxide is grown. By using selective epitaxy the heavily doped  $(n^+)$ , drain, source and p-type channel is created. This selective epitaxy removes overlap capacitance but high parasitic bipolar

gain remains problem. Moreover, other problems are creation of the high quality gate oxide on polysilicon and the controlling facets during selective capacity.

Figure 1-2: Vertical MOSFET based on selective epitaxy with reduced overlap capacitanc.

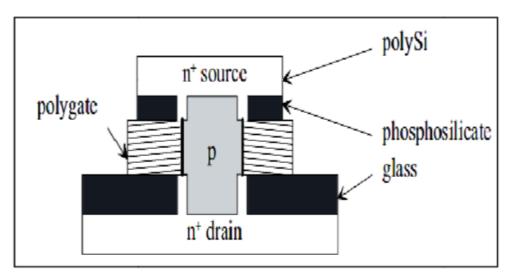

#### 1.2.2 Vertical replacement gate MOSFETs

The type 2 vertical MOSFETs is shown the figure 1-3 that is the vertical replacement gate MOSFETs (VRG). The VRG MOSFETs [11-14] can be made with competitive parasitic capacitances and packing density as compare to planar MOSFETs. Here, the layer deposition method is used to create a channel length which defined by the layer thickness. The gate length is precisely defined by a blanket film deposition. At first, arsenic ion is implanted into silicon wafer to form heavily doped (n–) drain regions. Then multi-layer stack of phosphosilicate glass (PSG)/ nitride/ undoped oxide/ nitride/ PSG is deposited on the drain layer. After the multilayer stack is deposited, a rectangular vertical trench is etched through the entire stack. Then boron-doped crystalline silicon is grown by selective epitaxy to form P-type single-crystal device channel. The silicon channel is planarized using chemical mechanical polishing (CMP). After this the process is followed by forming source region by arsenic ion implantation, forming source-drain extension (SDEs) by solid source diffusion (SSD), depositing and etching nitride spacer and removing sacrificial gate layer. Finally gate oxide is grown, gate deposition and patterning is done.

Figure 1-3: Vertical replacement gate MOSFET.

In this type of vertical MOSFETs, the overlap capacitances are much lower than the device, vertical MOSFETs based on epitaxy as it is determined by the thickness of the insulators between the PSG layers and the gate layer of this device. Because of source and drain extension across the entire width of the pillar, the parasitic bipolar transistor is found to be a problem. A partial solution is proposed by using a shallow polysilicon source pad to manufacture a leaky body contact [15]. Main disadvantage of this architecture is that it is not at all CMOS compatible due to the use of epitaxy.

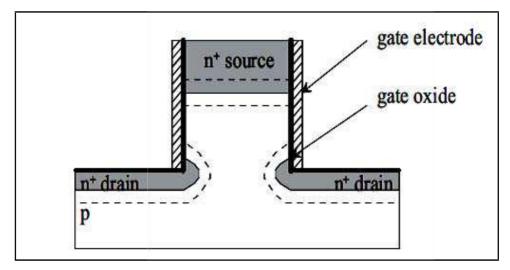

#### 1.2.3 Vertical MOSFETs based on ion implantation

Finally, the third type of vertical MOSFETs is the vertical MOSFETs based on ion-implantation [16-24] as illustrated in figure 1-4. The source and drain regions of this type of MOSFETs is formed by ion-implantation. The silicon pillar height and the implant energy determine the channel length of this type of MOSFETs.

Figure 1-4: Vertical MOSFET based on ion implantation.

In this type of MOS device it is possible to give a narrow shape pillar with the gate surrounding the entire pillar and the channel is completely lithography independent. In this type of device the parasitic bipolar gain is lower than the device, vertical MOSFETs base on epitaxy. The main reason of that is the drain never penetrates across the width of the pillar. Another major advantage of this type device is CMOS compatibility while parasitic source/ drain overlap capacitance has been eliminated in this type of vertical MOSFETs devices using FILOX process [25] which made this type of devices most promising for industrial application. Filox process introduces thick oxide both at pillar top and bottom thereby ensuring gate overlap with source/drain region introduces low overlap capacitances. Extensive investigations have been done on this type of vertical MOSFETs [26, 27, 28] and recently this type of vertical MOSFET has been demonstrated as viable route for improving RF performance of matured CMOS technologies [26].

#### **1.3** Thesis Objective:

In this thesis work we study the Process simulation of FILOX vertical MOSFET to estimate fabrication parameters for RF application. Different parameters are used to form 115nm channel length, 140nm Junction depth and 3.3nm gate oxide thickness for the fabrication of FILOX vertical MOSFET. This study would provide insight into choosing appropriate body doping and source/drain doping of  $2 \times 10^{20}$  cm<sup>-3</sup>. To get the desired body doping we see the alteration of channel length 115nm and junction depth 140nm. Then we adjusted the dose and energy of FILOX vertical MOSFET.

#### **1.4 Organization:**

This thesis report is segmented into four different chapters. The first chapter describes the introduction of this thesis includes the motivation, vertical MOSFET and its background, objective and organization.

In second chapter, the simulation methodology is described elaborately. Here, we discuss the basic simulation technique of device simulation software ATHENA-SILVACO. The second chapter also describes the Simulation overview and simulation profile.

The third chapter describes the results elaborately including detail steps with figure of a FILOX Vertical MOSFET fabrication process. Finally, it shows figure of different desired body doping and source drain doping.

Lastly, in fourth chapter we describe the conclusion.

## 2 CHAPTER: SIMULATION METHODOLOGY

#### 2.1 Simulation Overview

The device simulation is done using the commercial process simulator ATHENA - SILVACO. We describe of different desired body doping value for 115nm of channel length and 140nm of the junction depth, 3.3nm of gate oxide thickness and  $2\times10^{20}$  cm<sup>-3</sup> of source/drain doping FILOX vertical MOSFET. The heavily doped drain and source region were formed using uniform doping concentration of  $2\times10^{20}$  cm<sup>-3</sup> and the different desired body doping  $4\times10^{18}$  cm<sup>-3</sup>,  $2\times10^{18}$  cm<sup>-3</sup>,  $1\times10^{18}$  cm<sup>-3</sup>,  $8\times10^{17}$  cm<sup>-3</sup>,  $6\times10^{17}$  cm<sup>-3</sup>,  $4\times10^{17}$  cm<sup>-3</sup>,  $2\times10^{17}$  cm<sup>-3</sup>,  $8\times10^{16}$  cm<sup>-3</sup> and  $6\times10^{16}$  cm<sup>-3</sup> were used for analysis of this device structure. Here the body was p-type and source drain and gate were n-type with uniform concentration.

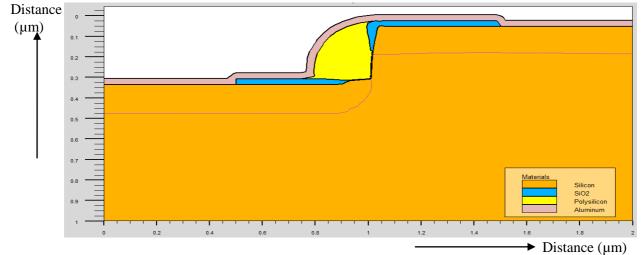

Figure 2-1: Schematic structure of FILOX vertical MOSFET.

To accurately create device grid structure, we ensured adequate mesh density in high field area such as channel region, source, drain and gate junction region. We have taken finer mesh at the interface of heavy doping and the light doping interface. We have removed grid lines from a specified device region where we expect a coarser grid using the ELIMINATE statement. A coarser grid is used at the substrate region in order to reduce simulation run time and achieve more accuracy. The created device grid structure is shown below,

#### 2.2 Simulation profile

Once the structure and the mesh were found to be as desired, the simulation was performed with appropriate models as discussed in section 2.1 and numerical solving methods. The model was invoked by using compress model, viscous model and Fermi model while keeping the accuracy of the simulation at an acceptable level.

#### 2.2.1 The compress model

The compress model is activated by specifying compress in the method statement before the diffuse statement and default the oxidation model. It is also recommended for simulation the planar and the non-planar structure where the stress is playing a minor effect to determining the oxide shape. The Compress Model is activated by specifying COMPRESS in the METHOD statement prior to a DIFFUSE statement. The Compress Model is the default oxidation model in SSUPREM4 [29].

Neglecting the acceleration and gravitational terms in the hydrodynamic flow equation, the creeping-flow equation is given by

$$\mu \nabla^2 \mathbf{V} = \nabla \mathbf{P} \tag{2.1}$$

where P is the hydrostatic pressure, V is velocity of oxide elements and  $\nabla$  is the oxide viscosity.

The oxide viscosity is calculated from the following equation:

$$\mu = \frac{YOUNG.M}{(2+2.POISS.R)}$$

(2.2)

where *YOUNG.M* is Young's modulus, which is specified in the MATERIAL statement, and *POISS.R* is Poisson's ratio, which is specified in the MATERIAL statement.

The oxide flow is treated as an incompressible fluid. By doing this, it implies the density of the oxide is constant with respect to time. Applying this fact to the mass continuity equation, the incompressibility condition is given as

$$\nabla . V = 0 \tag{2.3}$$

The incompressibility condition in Equation (2.3) is implemented by allowing a slight compressibility of the flowing oxide. Thus, Equation (2.3) is modified to give the following equation:

$$\nabla V = \frac{1 - (2 \cdot POISS.R)}{\mu}P$$

(2.4)

The solution of Equation (2.4) at each time step gives the velocity field of the flowing oxide elements. The Compress Model is recommended for simulations of planar and non-planar structures, where stress effects play a minor role in determining the oxide shape. When stress effects are important, you can use the Viscous oxidation model.

#### 2.2.2 The viscous model

The viscous model is activated by specifying the viscous parameter in the method statement before the diffuse statement. This model calculates stress in the growing oxide and almost the same shape for the si/oxide as the dose compress model. This model is activated by specifying the VISCOUS parameter in the METHOD statement prior to the DIFFUSE statement. The Viscous Model calculates stresses in the growing oxide and creates almost the same shape for the silicon/oxide interface as does the Compress model [29]. The stresses in the oxide are calculated as follows:

$$\sigma_{xx} + \sigma_{yy} = \frac{2 \cdot VISC \cdot 0 \cdot \exp\left(\frac{-VISC \cdot E}{kT}\right)}{1 - 2 \cdot POISS \cdot R} \left(\frac{\partial v_x}{\partial x} + \frac{\partial v_y}{\partial y}\right)$$

(2.5)

$$\sigma_{xx} - \sigma_{yy} = 2 \cdot VISC. 0 \cdot \exp\left(\frac{-VISC.E}{kT}\right) \left(\frac{\partial v_x}{\partial x} - \frac{\partial v_y}{\partial y}\right)$$

(2.6)

$$\sigma_{xy} = VISC. 0 \cdot \exp\left(\frac{-VISC. E}{kT}\right) \left(\frac{\partial v_x}{\partial x} + \frac{\partial v_y}{\partial y}\right)$$

(2.7)

where  $v_x$  and  $v_y$  are the *x* and *y* components of flow velocity *v* respectively. VISC.0 and VISC.E are the pre-exponential and activation energy, respectively for viscosity, are specified on the MATERIAL statement.

The stress calculated by the Viscous oxidation model replace stress that may have been previously generated by the STRESS.HIST parameter in the STRESS statement.

The stress-dependent nonlinear model based on Eyring's work [29] allows a description of the real shape of LOCOS profiles with kinks on the interface. The model is turned on by specifying the STRESS.DEP parameter the OXIDE statement. Using Equation (2.1) and Equations (2.4–2.7), the non-linear solver first finds a linear solution for flow velocities and stresses and then uses the stresses obtained to calculate the reduction factors for oxidant diffusivity,  $D_{eff}$ , oxide viscosity,  $\mu$ , and the interface reaction rate constant *k* as follows:

$$D^{(i)}eff = D^{(i-1)}eff \cdot \exp\left(\frac{V_d(\sigma_{xx} + \sigma_{yy})}{kT}\right)$$

(2.8)

$$\mu^{(i)} - \mu^{(i-1)} \frac{\left(\frac{\tau V_c}{2kT}\right)}{\sin h\left(\frac{\tau V_c}{2kT}\right)}$$

(2.9)

$$k^{(i)} = k^{(i-1)} \cdot \exp\left(-\frac{\sigma_r V_r + \sigma_t V_t}{kT}\right)$$

(2.10)

where *i* is the iteration.  $V_d$ ,  $V_c$ ,  $V_r$ , and  $V_t$  are the activation volumes (in Å<sup>3</sup>), specified in the OXIDE statement.

$\boldsymbol{\tau}$  is the total shear stress:

$$\tau = \frac{1}{2}\sqrt{(\sigma_{xx} - \sigma_{yy})^2 + 4\sigma_{xy}^2}$$

(2.11)

$\sigma_r$  is the normal component of the total stress:

$$\sigma_r = \sigma_{xx} n_x^2 + \sigma_{yy} n_y^2 + 2\sigma_{xy} n_x n_y$$

(2.12)

$\sigma_t$  is the tangential component of the total stress:

$$\sigma_t = \sigma_{xx} n_y^2 + \sigma_{yy} n_x^2 + 2\sigma_{xy} n_x n_y$$

(2.13)

where  $n_x$  and  $n_y$  are the x and y components of the unit vector normal respectively. The reduced parameters feed back to the next iteration. This process continues until the accuracy criterion is met. Fast convergence of this process is not guaranteed. Oxidation calculations by the stress-dependent model usually take much more CPU time than the Compress Model.

#### 2.2.3 The Fermi Model

The Fermi Model assumes that point defect populations are in thermodynamical equilibrium and thus need no direct representation. All effects of the point defects on dopant diffusion are built into the pair diffusivities. The main advantage for using the Fermi Diffusion model is it will greatly improve the simulation speed, since it does not directly represent point defects and only needs to simulate the diffusion of dopants. Also, the Fermi Model usually results in an easier numerical problem due to the avoidance of "numerical stiffness". But since point defects are not directly simulated, the Fermi model cannot deal with certain process conditions in which the defect populations are not in equilibrium, such as in wet oxidation (where Oxidation Enhanced Diffusion (OED) is important), emitter-base diffusions and wherever implantation results in an initial high level of implant damage. In the Fermi Model, each dopant obeys a continuity equation of the form:

$$D_{AX}\left(T.\frac{n}{n_i}\right) = D_{AX}^{X} + D_{AX}^{-}\left(\frac{n}{n_i}\right)^1 + D_{AX}^{-}\left(\frac{n}{n_i}\right)^2 + D_{AX}^{+}\left(\frac{n}{n_i}\right)^{-1} + D_{AX}^{++}\left(\frac{n}{n_i}\right)^{-2}$$

(2.14)

where  $C_{Ch}$  is the chemical impurity concentration,  $Z_A$  is the particle charge (+1 for donors and -1 for acceptors),  $D_{AV}$  and  $D_{AI}$  are the joint contributions to the dopant diffusivity from dopant-vacancy and dopant-interstitial pairs in different charge states.  $C_A$  is the mobile impurity concentration and *E* is the electric field.

The terms  $D_{AV}$  and  $D_{AI}$  depend on both the position of the Fermi level as well as temperature and are expressed as:

$$D_{AX}^{c} = D. 0_{AX}^{c} \exp\left(-\frac{D. E_{AX}^{c}}{kT}\right)$$

(2.15)

where the temperature dependency is embedded in the intrinsic pair diffusivities, which are specified by Arrhenius expressions of the type:

$$\frac{\partial C_{Ch}}{\partial t} = \sum_{X=I,V} \nabla \cdot D_{AX} \left( \nabla C_A - Z_A C_A \frac{qE}{kT} \right)$$

(2.16)

Table 2-1 shows the names of the pre-exponential factors, D.0, and activation energies, D.E, for each of the charge states, c, of the various intrinsic pair diffusivity terms [29].

Pair charge states beyond two are unlikely to occur, which is why they have been omitted. Also, for most dopants it is seldom that more than three of the terms above are non-vanishing.

| Pair | Charge State | Preexponential<br>factor | Activation Energy |

|------|--------------|--------------------------|-------------------|

| AV   | Х            | DVX.0                    | DVX.E             |

| AV   | -            | DVM.0                    | DVM.E             |

| AV   | =            | DVMM.0                   | DVMM.E            |

| AV   | +            | DVP.0                    | DVP.E             |

| AV   | ++           | DVPP.0                   | DVPP.E            |

| AI   | Х            | DIX.0                    | DIX.E             |

Table 2-1. Table of intrinsic pair diffusivities for different pair types

| Pair | Charge State | Preexponential<br>factor | Activation Energy |

|------|--------------|--------------------------|-------------------|

| AI   | -            | DIM.0                    | DIM.E             |

| AI   | =            | DIMM.0                   | DIMM.E            |

| AI   | +            | DIP.0                    | DIP.E             |

| AI   | ++           | DIPP.0                   | DIPP.E            |

#### **3 CHAPTER: RESULT**

#### 3.1 FILOX vertical MOSFET Fabrication Process

To create the vertical MOSFET structure we follow some instructions such as, A silicon wafer is taken as the starting material and a p-type body is formed by boron implantation having a boron dose of  $5.0 \times 10^{14}$  cm<sup>-2</sup> and high-temperature drive-in with energy of 50 key. Channel length is produced by varying the Si pillar with the help of dry etch, having a pillar height of 300nm. A sacrificial oxidation was performed to eliminate dry etch damage and reduce the surface roughness on the pillar sidewall. For the FILOX process a silicon nitride was deposited and anisotropically etched to create a nitride spacer. The nitride pacer is etched with the help of dry etch according to the desired shape. A FILOX oxide layer was thermally grown having a thickness of 60 nm. Arsenic implantation is performed then the source and drain are implanted. The nitride fillet and pad oxide are subsequently removed by wet etch afterward gate oxide is grown. A polysilicon gate is deposited and patterned by dry etch to create a surround gate. A rapid thermal annealing is done. Finally source and drain are patterned for metal contacts and aluminum contacts are formed. Final body doping was  $4 \times 10^{18}$  cm<sup>-3</sup> and source/drain doping were  $2 \times 10^{20}$  cm<sup>-3</sup>. FILOX vertical MOSFET fabrication steps are shown in the figures below,

**Figure 3-1**: Net doping  $5.0 \times 10^{14}$  cm<sup>-3</sup> of silicon wafer of FILOX vertical MOSFET.

**Figure 3-2**: Net doping  $1.0 \times 10^{18}$  cm<sup>-3</sup> by implanted with boron dose= $5 \times 10^{14}$  cm<sup>-2</sup> of and energy=50 kev of silicon wafer of FILOX vertical MOSFET.

**Figure 3-3**: Net doping  $1.0 \times 10^{19}$  cm<sup>-3</sup> after drive in. Distance (µm)

Figure 3-4: All the oxides are stripped.

**Figure 3-5**: 300nm pillar formation using dry etch.

Figure 3-6: Deposition of pad oxide oxide=10 nm on the Pillar.

**Figure 3-7**: Deposition of Nitride Spacer =70nm on pad oxide.

Figure 3-8: After dry etching of nitride spacer.

Figure 3-9: After etch of pad oxide.

Department of Electrical and Electronic Engineering

**Figure3-11**: Implantation of Arsenic dose= $6 \times 10^{15}$  cm<sup>-2</sup> and energy=90 kev of n-type source and drain.

Figure 3-12: Removal of nitride fillet.

Figure 3-13: Wet etch of oxide from sidewalls of pillar.

**Figure 3-14**: Deposition of gate oxide of thickness 3.3nm.

Figure 3-15: Deposition of polysilicon of 200nm thickness.

Figure 3-16: Formation of polysilicon gate by dry etch.

Figure 3-17: After rapid thermal Annealing using Fermi compress.

Figure 3-18: Pattern of source and drain for metal contact of FILOX vertical MOSFET.

Figure 3-19: Aluminum deposition and etching to create S/D, gate contact formation of FILOX vertical MOSFET.

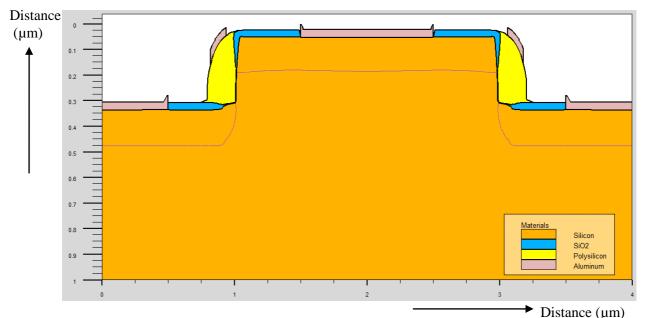

Figure 3-20: Right mirror and Complete structure of FILOX vertical MOSFET.

#### 3.2 Process parameter for desired different Body and S/D doping values

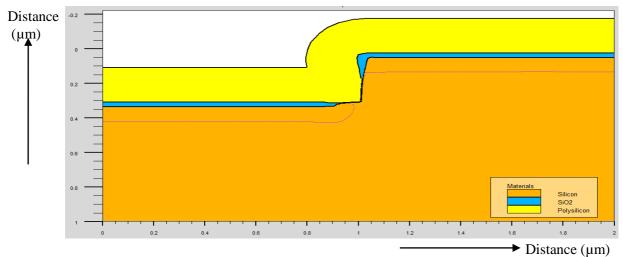

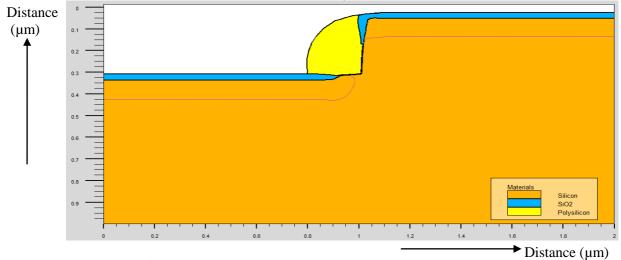

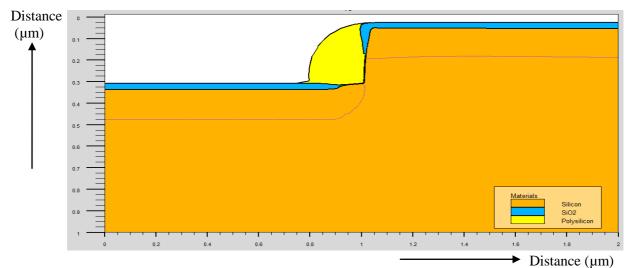

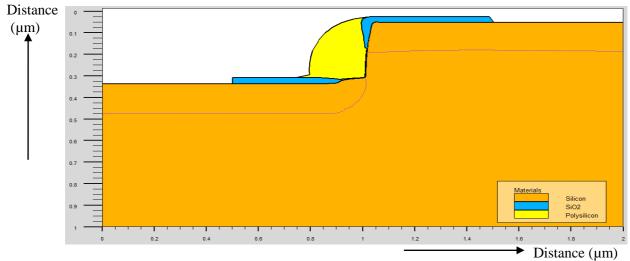

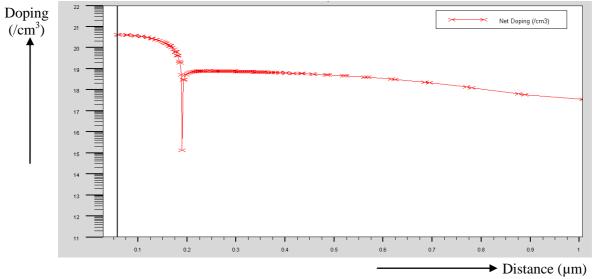

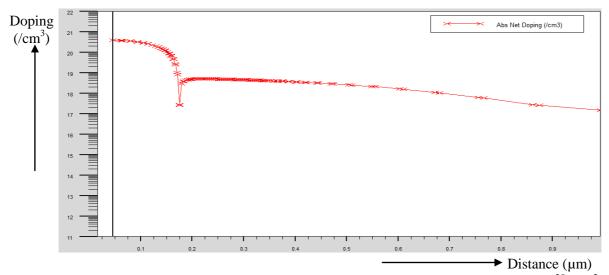

This section describes figure of different desired body doping values for 115nm channel length, 140nm junction depth and  $2 \times 10^{20}$  cm<sup>-3</sup> of source/drain doping of FILOX vertical MOSFET. For each body doping several random simulations required for adjusting dose anneal time. Change of body doping also changes S/D junction depth and hence we need to change S/D doping as well. Following figures show realized device doping profile from pillar top.

**Figure 3-21**:115 channel length FILOX vertical MOSFET with S/D doping  $2 \times 10^{20}$  cm<sup>-3</sup> and net body doping of  $4 \times 10^{18}$  cm<sup>-3</sup>.

**Figure 3-22**: 115 channel length FILOX vertical MOSFET with S/D doping  $2 \times 10^{20}$  cm<sup>-3</sup> and net body doping of  $2 \times 10^{18}$  cm<sup>-3</sup>.

**Figure 3-23**:115 channel length FILOX vertical MOSFET with S/D doping  $2 \times 10^{20}$  cm<sup>-3</sup> and net body doping of  $1 \times 10^{18}$  cm<sup>-3</sup>.

Figure 3-24: 115 channel length FILOX vertical MOSFET with S/D doping 2×10<sup>20</sup> cm<sup>-3</sup> and net body doping of 8×10<sup>17</sup> cm<sup>-3</sup>.

**Figure 3-25**: 115 channel length FILOX vertical MOSFET with S/D doping  $2 \times 10^{20}$  cm<sup>-3</sup> and net body doping of  $6 \times 10^{17}$  cm<sup>-3</sup>.

**Figure 3-26**:115 channel length FILOX vertical MOSFET with S/D doping  $2 \times 10^{20}$  cm<sup>-3</sup> and net body doping of  $4 \times 10^{17}$  cm<sup>-3</sup>.

**Figure 3-28**:115 channel length FILOX vertical MOSFET with S/D doping  $2 \times 10^{20}$  cm<sup>-3</sup> and net body doping of  $1 \times 10^{17}$  cm<sup>-3</sup>.

**Figure 3-29**: 115 channel length FILOX vertical MOSFET with S/D doping  $2 \times 10^{20}$  cm<sup>-3</sup> and net body doping of  $8 \times 10^{16}$  cm<sup>-3</sup>.

**Figure 3-30**: 115 channel length FILOX vertical MOSFET with S/D doping  $2 \times 10^{20}$  cm<sup>-3</sup> and net body doping of  $6 \times 10^{16}$  cm<sup>-3</sup>.

#### **4** CHAPTER

#### 4.1 CONCLUSION

In this thesis, we observe process simulation of FILOX vertical MOSFET to estimate fabrication parameters. A simple self-aligned process has been developed to reduce the parasitic overlap capacitance in vertical MOSFETs using nitride spacers on the sidewalls of the trench or pillar and a local oxidation. We describe different step of FILOX vertical MOSFET Fabrication and finally we get 115nm of channel length, 140nm of the junction depth, gate 3.3nm of oxide thickness,  $4 \times 10^{18}$  cm<sup>-3</sup> of body doping and  $2 \times 10^{20}$  cm<sup>-3</sup> of source/drain doping in the FILOX vertical MOSFET. To get the desired body doping we see the alteration of channel length 115nm and junction depth 140nm. Then we adjusted the dose and energy of FILOX vertical MOSFET.

#### 4.2 Table

This section describes result of desired body doping value for 115nm of channel length and 140nm of the junction depth and  $2 \times 10^{20}$  cm<sup>-3</sup> of source/drain doping FILOX vertical MOSFET. We observe desired body doping below in the table,

|       | Dose                 | Energy | Channel    | Doping(Body)       |

|-------|----------------------|--------|------------|--------------------|

|       | $(cm^{-2})$          | (kev)  | length(nm) | $(cm^{-3})$        |

| i.    | 5.0×10 <sup>14</sup> | 50     | 115        | 4×10 <sup>18</sup> |

| ii.   | 3.0×10 <sup>14</sup> | 45     | 115        | 2×10 <sup>18</sup> |

| iii.  | $2.0 \times 10^{14}$ | 30     | 115        | 1×10 <sup>18</sup> |

| iv.   | $1.4 \times 10^{14}$ | 27     | 115        | 8×10 <sup>17</sup> |

| V.    | $1.0 \times 10^{14}$ | 26     | 115        | 6×10 <sup>17</sup> |

| vi.   | $0.9 \times 10^{14}$ | 13     | 115        | 4×10 <sup>17</sup> |

| vii.  | 3.6×10 <sup>13</sup> | 52     | 115        | 2×10 <sup>17</sup> |

| viii. | 3.0×10 <sup>13</sup> | 44     | 115        | 1×10 <sup>17</sup> |

| ix.   | $1.4 \times 10^{13}$ | 55     | 115        | 8×10 <sup>16</sup> |

| х.    | $1.4 \times 10^{13}$ | 48     | 115        | 6×10 <sup>16</sup> |

Table 4-1 for p-type implant:

## Table 4-2 for n-type implant:

|       | Dose                 | Energy | Junction  | Doping(S/D)        |

|-------|----------------------|--------|-----------|--------------------|

|       | $(cm^{-2})$          | (kev)  | depth(nm) | $(cm^{-3})$        |

| i.    | $6.0 \times 10^{15}$ | 90     | 140       | $2 \times 10^{20}$ |

| ii.   | $6.0 \times 10^{15}$ | 85     | 140       | $2 \times 10^{20}$ |

| iii.  | $6.0 \times 10^{15}$ | 84     | 140       | $2 \times 10^{20}$ |

| iv.   | 6.0×10 <sup>15</sup> | 82     | 140       | $2 \times 10^{20}$ |

| V.    | $6.0 \times 10^{15}$ | 80     | 140       | $2 \times 10^{20}$ |

| vi.   | 6.0×10 <sup>15</sup> | 78     | 140       | $2 \times 10^{20}$ |

| vii.  | $6.0 \times 10^{15}$ | 76     | 140       | $2 \times 10^{20}$ |

| viii. | $5.6 \times 10^{15}$ | 76     | 140       | $2 \times 10^{20}$ |

| ix.   | $5.5 \times 10^{15}$ | 70     | 140       | $2 \times 10^{20}$ |

| Х.    | $5.5 \times 10^{15}$ | 69     | 140       | $2 \times 10^{20}$ |

## REFERENCES

- J. Moers, S. Trellenkamp, L. Vescan, M. Marso, P. Kordos, and H. Lueth, "Vertical double-gate MOSFETs based in epitaxial growth by LPCVD," ESSDERC, pages 191-194, 2001.

- [2] V.R. Rao, F. Wittmann, H. Gossner and I. Eisele, "Hysteresis behavior in 85-nm channel length vertical n-MOSFETs grown by mbe," IEEE Trans. Electron Device, 43(6): 973-976, June 1996.

[3] T. Aeugle, L. Risch, H. Schaefer, M. Franosch, M. Eller and T. Ramcke, "Fabrication of ultrashort vertical mos-transistors," proc.6<sup>th</sup> int. Symp. Of ultra Large Scale VLSI Science and Technology, Electrochem. Soc., pennington NJ, pages 561-569, 1997.

- [4] S. Trellenkamp, j. Moers, A. van der Hart, P. Kordos, and H. Lueth, "Process steps for a double gate MOSFETs with vertical layout," ASDAM, 2002.

- [5] L. Risch, T. Aeugle, and W. Roesner, "Recent progress with vertical transistors," ESSDERC, pages 34-41, 1997.

- [6] D. Klaes, J. Moers, A. Toennesmann, S. Wickenhaeuser, L. Vescan, M. Marso, T.Grabolla, M. Grimm and H. Luet, "Selectively grown vertical si mos transistor with reduvced overlap capacitances," Thin Solid Films, (336):306-308, 1998.

- [7] J. Moers, A. Toennesmann, D. Klaes, L. Vescan, A. van der Hart, A. Fox, M. Marso, P. Kordos, and H. Luet, "Vertical silicon MOSFETs based on selective epitaxial growth," ASDAM Advanced Semiconductor Devices and Microsystems, pages 67-70, 2000.

- [8] D. Behammer, L. Vescan, R. Loo, J. Moers, A. Mueck, H. Luet, and T. Grabolla, "Selectively growth vertical si-p mos transistor with short channel lengths," Electronics Lett., 32(4):406-407, February 1996.

- [9] J. Moers, D. Klaes, A. Toennesmann, L. Vescan, S. Wickenhaeuser, T. Grabolla, M.Marso, P. Kordos, and H. Luet, "Vertical pMOSFETs with gate oxide deposition before selective epitaxial growth," Solid State Electronics, 43:529-535, 1999.

- [10] J. Moers, D. Klaes, A. Toennesmann, L. Vescan, S. Wickenhaeuser, M. Marso, P.Kordos, and H. Luet, "19ghz vertical si p-channel MOSFETs," Electronics Lett. 35(3):239-240, February 1999.

- [11] J.M. Hergenrother, T. Nigam, D. Monroe, F.P. Klemens, et al., "50nm vertical replacement-gate (VRG) nMOSFETs with ald hfo2 al203 gate dielectric," IEDM. 2001.

- [12] D. Monroe, J.M. Hergenrother, "The vertical replacement-gate (VRG) process for scalable general- purpose complementary logic," ISSCC Tec Dig 2000:134.

- [13] Oh S-H et al., "50 nm Vertical replacement-gate (VRG) pMOSFETs," IEDM Tec Dig 2000:65.

- [14] J.M. Hergenrother, Sang–Hyun Oh, T. Nigam, D.Monroe, F. P. Klemens, A. Kornblit, "The vertical replacement-gate (VRG) pMOSFETs," Solid State Electronics, 46(2002) 939-950,

- [15] J.M. Hergenrother, D. Monroe, F.P. Klemens, A. Kornblit, and G.R. Weber et al, "The vertical replacement-gate (VRG) MOSFET: A 50 nm vertical MOSFETs with lithography independent gate length," IEDM, pages 75-78, 1999.

- [16] B. Goebel, J. Luetzen, D. Manger, P. Moll, K. Muemmler, M. Popp, U. Scheler, T.Schloesser, H. Seidl, M. Sesterhenn, S. Slesazeck, and S. Tegen, "Fully depleted surround gate transistor (sgt) for 70nm dram and beyond," IEDM, 2002.

- [17] T. Schulz, W. Roesner, L. Risch, and Adam Korbel, "Short channel vertical sidewall MOSFETs," IEEE trans. Electron Device, 48(8):1783-1788, August 2001.

- [18] C.P. Auth and J.D. Plummer, "Vertical, fully deplated, surround gate MOSFETs on sub-0.1um thick pillars," Device research Conference, pages 172-175, 1996.

- [19] M. Masaharam, T. Matsukawa, K. Ishii, and Y. Liu et al. "Si nanoprocess for vertical double gate MOSFETs fabrication," Microprocesses and Nanotecnology Conference, 2002.

- [20] B. Goebel, D. Schumann, and E. Bertagnolli, "Vertical n-channel MOSFETs for extremely high density memories: the impact of interface orientation and device performance," IEEE Trans. Electron Device 48(5):897-906, May 2001.

- [21] T. Schulz, W. Roesner, L. Risch, and U. Langmann, "50nm vertical sidewall transistors with channel doping concentrations," IEDM, pages 61-64, 2000.

- [22] A. Nitayama, K. Sunouchi, N. Okabe, K. Sunouchi, K. Hieda F. Horiguchi, and F.Masuoka, "Multi-pillar surrounding gate transistor (m-sgt) for compact and high speed circuits," IEEE Trans. Electron Device, 38(3): 579-583, March 1991.

- [23] T. Schulz, W. Roesner, L. Risch, and U.Langmann, "Short channel vertical sidewall transistors," ESSDERC, pages 552-555, 2000.

- [24] H. Takato, K.Sunouchi, N. Okabe, A. Nitayama, K. Hieda F. Hori guchi, and F. Masuoka, "Impact of surrounding gate transistor (sgt) for ultra-highdensity lsi's," Electron Device, 38(3):573-578, March 1991.

- [25] V. D. Kunz, T. Uchino, C. H. de Groot, P. Ashburn, D. C. Dnaghy, S. hall, Y. Wang, and P.L.F. Hemment, "Reduction of parasitic capacitance in vertical MOSFETs by spacer local oxidation," IEEE Trans. Electron Devices, pp.897-900, June, 2003.

- [26] M.M.A. Hakim, L. Tan, A. Abuelgasim, K. Mallik, S. Connor, A. Bousquet, C. H. de Groot, W. Redman-White, S. Hall and P. Ashburn, "Self-Aligned Silicidation of Sorround Gate vertical MOSFETs for Low Cost RF Applications," IEEE Trans. Electron Devices, VOL. 57, No.12, December 2010.

- [27] M.M.A. Hakim, A. Abuelgasim, L. Tan, C. H. de Groot, W. Redman-White, S. Hall and P. Ashburn, "Improved Drive Current in RF Vertical MOSFETs Using Hydrogen Anneal," IEEE Trans. Electron Devices, VOL. 32, No. 3, March 2011.

- [28] M.M.A. Hakim, L. Tan, O. Buiu, W. Redman-White, S. Hall, and P. Ashburn, "Improved sub-threshold slope in short-channel vertical MOSFETs using FILOX oxidation," Solid-State Electronics, 53(2009) 753-759.

- [29] ATHENA User's Manual : 2D PROCESS SIMULATION SOFTWARE.

- [30] Y.Taur and T. Ning, "Fundamental of Modern VLSI Devices," Cambridge University Press, Cambridge, 1998.